2nmで設計の限界がくる

2nmプロセスはすでにTSMCやSamsungが試作チップを顧客へ提供し、製造技術としては実用段階に入りつつあります。

しかし、サンプルが動作したからといって、2nm世代の課題が解決したわけではありません。

むしろ、本格的な製品設計に進む段階で“設計側の限界”がより鮮明に浮かび上がっています。

これまで微細化の壁といえば、露光や材料といった「製造技術」の課題が中心でした。

しかし2nmでは、製造が成立しても、それを使いこなすための設計フロー全体が先に破綻すると指摘されています。

背景には、物理限界がもたらす複数の負荷が同時に押し寄せる構造があります。

- 配線抵抗・RC遅延・IRドロップの急増により、配線が性能の律速段階となる

- マスク枚数や設計ルールの複雑化で工数が指数関数的に増大

- 検証工程の肥大化により、設計工数の大半が動作確認に費やされる

これらはすべて「設計密度」という一つのテーマに収束します。

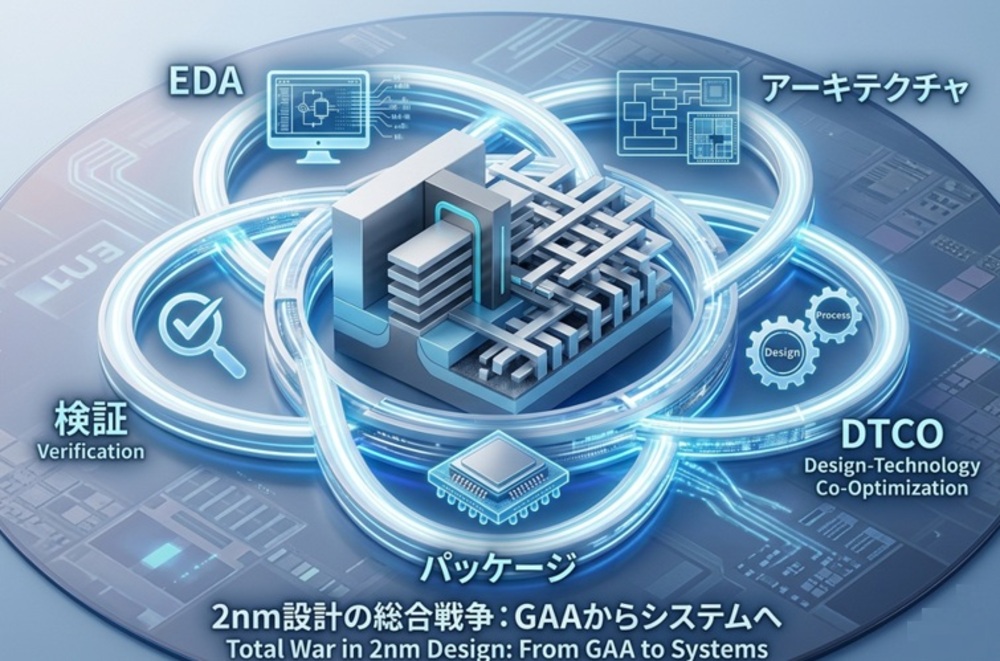

2nmでは、アーキテクチャ、DTCO、3DICパッケージ、EDA、検証が強く結びつき、どれか一つの改善では設計が成立しません。

サンプルが存在する今こそ、製造より設計がボトルネックになる構造がより明確になっているのです。

本コラムでは、2nm設計がなぜここまで困難なのか、そしてNVIDIAやAppleといった先端企業がどのようにこの壁を突破しているのかを5つの視点から解説します。

2nmは「製造の時代」から「設計力が競争力を決める時代」への決定的な転換点なのです。

本コラムは連載の第5回目です。

・第1回:AIチップの2nm競争は“配線密度”で決まる HBM・RDL・BSPDNが変える半導体構造

・第2回:【2026年最新】AI-DCは“電力密度限界”で崩壊かー電力・消費電力・電源設計の本質

・第3回:HBMはなぜ“足りない”のか ― 需給逼迫の裏にある「製造+性能」限界の宿命

・第4回:CoWoSとHBM不足の真因:TSMC・Intel・Samsungの覇権争いと2035年AIパッケージロードマップ

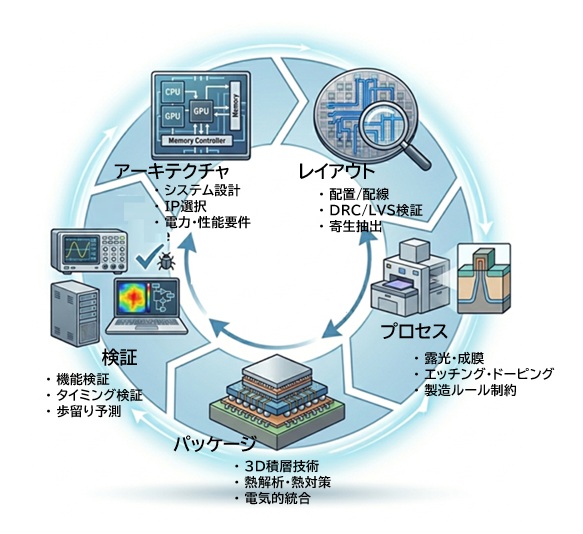

アーキテクチャ:PPAを決める“設計思想”の限界

2nmでは、アーキテクチャの選択が最終的なPPA(性能・電力・面積)の大半を左右します。

これまでのようにEDAツールで後から調整する余地は小さく、設計思想そのものが良くなければ後工程で挽回できない段階に入っています。

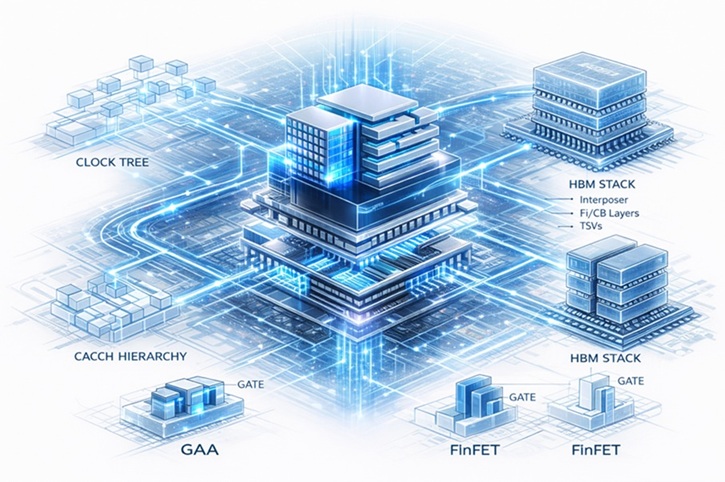

GAA時代に求められる新しい設計ルール

2nmで本格導入されるGAA(Gate-All-Around)は電流制御を改善する一方、設計側には新たな最適化を要求します。

- クロック設計の再構築

GAAの特性を活かすには、FinFET時代とは異なるクロックツリーが必要になる。 - キャッシュ階層の再設計

演算性能に対しメモリ応答が追いつかない「メモリの壁」が強まり、階層構造の見直しが不可欠。 - HBM前提のアーキテクチャ

AIチップでは帯域が律速となるため、HBMを中心に据えた構成が標準化する。

“アーキの悪さ”が歩留まりを直撃する時代

2nmでは配線遅延が支配的となり、特にGPUのような大規模チップではアーキテクチャの構造が性能限界を決めます。

そのため、パーティショニング(分割戦略)が極めて重要になります。

巨大なモノリシックダイよりも、機能を分割したチップレット化が主流となりますが、分割が不適切だとデータ流れが破綻し、性能低下だけでなく歩留まり悪化にも直結します。

つまり、2nmでは賢いアーキテクチャこそ最大のコスト削減策です。

どれほどEDAが進化しても、土台となる構想が誤っていれば物理限界は突破できません。

設計の勝敗は、コードを書く前の“構想段階”で決まる時代に入っています。

DTCO:プロセスと設計の同時最適化が必須に

2nmでは、設計者が製造ルールに従って回路を描くだけではチップは成立しません。

プロセスと設計を同時に最適化するDTCO(Design-Technology Co-Optimization)が不可欠です。

2nmがDTCOを必要とする理由

微細化が2nmに到達すると、これまで無視できた誤差が致命的な性能劣化や歩留まり低下につながります。

- 配線抵抗の急増とバリア層の相対肥大化

配線が細くなるほど抵抗が跳ね上がり、バリア層が相対的に厚くなることで電流経路が極端に狭くなる。 - GAAのしきい値制御の難易度上昇

GAA構造では、しきい値電圧のばらつきが性能と電力効率を大きく左右する。 - BSPDN(裏面電源供給)の導入

電源線を裏面に移すことで性能向上が期待できる一方、設計と製造の複雑性が飛躍的に増す。

設計と製造の境界は存在しなくなる

DTCOが扱う範囲は、従来のレイアウト設計を大きく超えています。

- 配線層スタックの最適化

各層の配線太さ・配置をプロセス制約と照らし合わせて決定する。 - 電源ネットワークとマスク制約の統合設計

複雑化する電源網を効率的に配置しつつ、EUVのマスク制約を満たす必要がある。 - DFM(製造容易性設計)の深化

回路が動くだけでなく、歩留まり良く安定して量産できる設計が求められる。

もはや「設計が終わったら工場へ渡す」という分業モデルは成立しません。

2nmでは、設計者とプロセスエンジニアが互いの専門分野に踏み込み、同じ問題を共有しながら最適解を探るアクションが必須です。

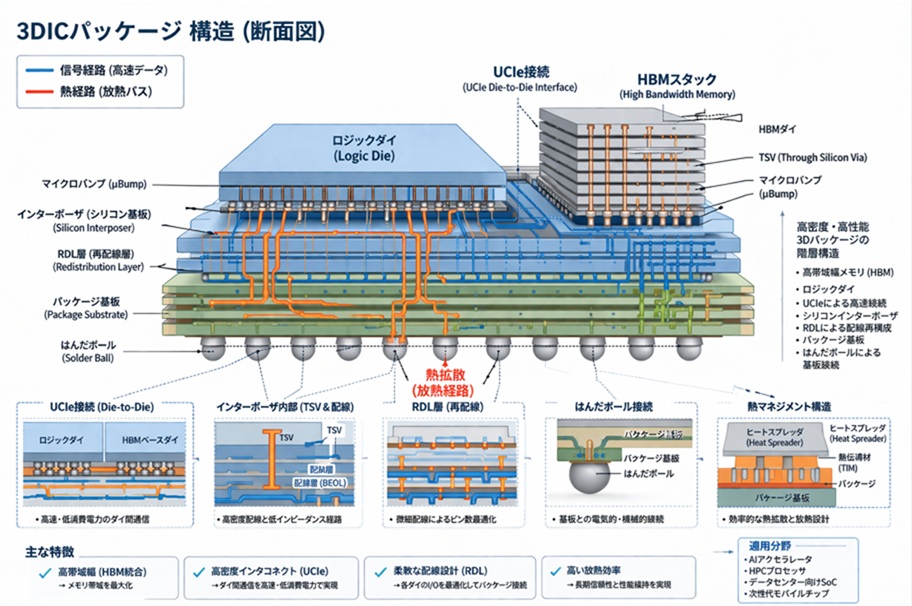

パッケージ:3D-ICが設計の中心となる

2nm時代の設計は、もはやシリコンダイ内部だけでは完結しません。

従来は後工程とされてきたパッケージングが、今や設計の中心要素へと位置づけを変えています。

3D-ICやチップレット化の進展により、パッケージとロジック設計の境界は急速に曖昧になっています。

パッケージの“前工程化”と境界の崩壊

TSMCのCoWoS、IntelのFoverosなどの先端パッケージ技術により、パッケージはロジック設計の延長として扱われるようになりました。

- RDL配線の進化

再配線層(RDL)がチップ間通信を担い、ロジックの一部として機能する。 - インターポーザの影響増大

インターポーザの抵抗・遅延がPPAに直接影響し、設計上の主要パラメータとなる。 - UCIeによる標準化

異なるダイを組み合わせるチップレット設計が一般化し、パッケージがシステム統合の基盤となる。

※UCIe(Universal Chiplet Interconnect Express)とは、 異なるメーカー・異なるプロセスで作られたチップレット同士を、同一パッケージ内で高速・低消費電力に接続するための「オープン標準規格」

チップレット化がもたらす新たな設計課題

チップレット化は歩留まり改善に有効ですが、設計の難易度を大幅に引き上げます。

- 熱と応力の管理

3D積層では熱がこもりやすく、熱ボトルネックが性能を制約する。 - 物理的歪みの解析

異なる素材を積層するため、熱膨張差による反りや応力解析が不可欠となる。

2nm以降の設計では、ロジック単体の最適化では不十分です。 電源、信号、熱、機械的強度まで含めた“パッケージ全体のシステム設計” が、最終的な製品品質と性能を左右します。

パッケージはもはや後工程ではなく、設計戦略の中核そのものです。

EDA:設計自動化の限界とAI化の現実

2nmという極微細領域では、EDA(Electronic Design Automation)ツールがこれまで以上に大きな壁に直面しています。

設計の複雑さがツールの処理能力を上回り、従来の自動化では設計が収束しないケースが増えています。

今、設計現場ではAIによる最適化が現実的な選択肢として急速に広がっています。

関連記事:2035年のEDA覇権:三強の未来戦略と新興勢力の可能性、そして市場成長の行方

EDAが直面する“2nmの壁”

従来はEDAツールに回路情報を与えれば、時間をかけて最適な配置配線(P&R)が得られました。

しかし2nmでは物理的制約が強まり、ツールが解を見つけられない事態が頻発します。

- 配線遅延の支配

配線抵抗とRC遅延が性能を決定づけ、タイミングクロージャの難易度が急上昇する。 - EUVダブルパターニングの制約

複数回露光が必要となり、マスク制約がレイアウト自由度を大きく奪う。

AI設計(DSO.ai / Cerebrus)の台頭

こうした複雑性を突破するため、強化学習を用いたAI設計ツールが導入されています。

- PPAの改善

AIが膨大な設計空間を探索し、人間では到達できない配置配線を提示する。 - 設計期間の短縮

数週間かかっていた最適化作業を数日に圧縮し、開発コストを削減。 - マスク最適化の自動化

露光制約を考慮したレイアウト生成を自動化し、設計負荷を軽減。

AIでも越えられない“物理の壁”

ただしAIは万能ではありません。

計算で最適化できても、物理限界そのものを消すことはできません。

- RC遅延・配線抵抗

材料特性に起因する抵抗や遅延は、アルゴリズムでは根本解決できない。 - 3D-ICの熱・応力解析

熱管理や歪み解析は高度な物理シミュレーションと設計者の経験が不可欠。

2nm設計においてEDAは依然として中心的役割を担いますが、ツール単独では限界が明確です。

アーキテクチャ、DTCO、パッケージとの緊密な連携があって初めて、EDAとAIの力が最大限に発揮されます。

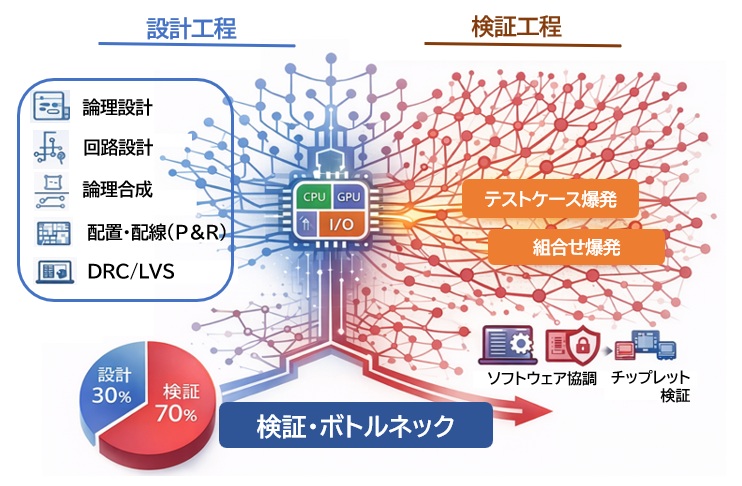

検証:設計工数の70%を占める“真のボトルネック”

2nm設計で最も深刻な負荷となっているのは、回路を描く作業ではなく、設計が意図通り動くかを確認する検証(Verification)工程です。

先端チップでは開発工数の約70%が検証に費やされ、設計全体の律速段階となっています。

2nmで検証が“爆発”する理由

2nmでは、設計規模と複雑性が飛躍的に増し、検証すべき項目が天文学的な量に膨れ上がります。

- アーキテクチャの複雑化

トランジスタ数と機能が増大し、テストケースが指数関数的に増える。 - チップレット化による組み合わせ爆発

複数ダイ間の通信・同期を確認する必要があり、組み合わせパターンが膨大になる。 - ソフトウェアとの協調検証

ハードとソフトを同時に検証するシステムレベルの確認が必須となる。 - セキュリティ検証の増加

脆弱性やサイドチャネル対策など、追加の検証項目が急増している。

検証技術の進化と、それでも残る“検証地獄”

膨大な検証負荷に対応するため、技術も進化しています。

- 形式検証(Formal Verification)

数学的手法で仕様との一致を論理的に証明する。 - エミュレーション/FPGAプロトタイピング

実機に近い速度でソフトを動かし、動作を早期に確認する。 - AIによるバグ検出

過去データを基にバグの潜在箇所を推定し、検証の優先順位を最適化する。

しかし、これらを駆使しても2nmの設計密度は依然として高く、検証は“地獄”と呼ばれるほどの負荷を生み続けています。

もはや検証は単なる確認作業ではなく、設計進行を左右する最大のボトルネックとなっています。

2nm設計は「総合戦争」となる

2nm設計が従来世代と決定的に異なるのは、アーキテクチャ、DTCO、パッケージ、EDA、検証という5つの要素がもはや独立した工程ではなく、強く結びついた一体構造になっている点です。

どれか一つを変更すれば、他の領域に連鎖的な影響が生じます。

5つの要素が互いに依存し合う連鎖

2nmでは、各工程がドミノのように相互作用し、単独最適化が成立しません。

- アーキテクチャ ↔ DTCO アーキの選択がDTCOの最適化方針を大きく左右する。

- DTCO ↔ EDA 新しい製造ルールは即座にEDAアルゴリズムへ反映される必要がある。

- EDA ↔ 検証 自動化が進むほど生成される回路が複雑化し、検証手法の高度化が不可欠となる。

- パッケージ ↔ アーキテクチャ 3DICやチップレット技術の進化が、最適なチップ分割戦略へフィードバックされる。

すべての“密度”が絡み合う戦場

2nm設計では、複数の密度が極限まで高まり、どれか一つを優先すると他が犠牲になる構造が生まれます。

- 設計密度 × 配線密度

限られた面積に機能を詰め込みつつ、信号遅延を抑える必要がある。 - 電力密度 × 熱密度

高密度化による発熱を抑え、効率的に冷却する設計が求められる。 - I/O密度

チップ間・外部との通信帯域を確保しつつ、物理的制約を満たす必要がある。

これらは互いにトレードオフの関係にあり、単一技術で突破できる問題ではありません。

2nm以降の設計は、複数領域を同時に俯瞰し、全体最適を追い続ける“総合戦争”そのものです。

2nm以降の設計戦略 ― 勝者はどう動くか

2nm設計は、もはや一企業だけで完結できる領域ではありません。

アーキテクチャ、EDA、DTCO、パッケージ、検証を横断する巨大なエコシステムをどう構築し、どれだけ早く深く統合できるかが勝敗を分けます。

その中で、先端企業には共通する“3つの勝ち筋”が見えてきます。

生き残るための3つの勝ち筋

- AI × EDAの徹底活用

人間の探索能力を超えるAI最適化を設計フローの中心に据え、膨大な設計空間を高速に探索する。 - アーキテクチャの抜本的転換

モノリシックに固執せず、チップレットや3DICを前提とした分割・統合戦略へ移行する。 - DTCOの深化

プロセス開発の初期段階から設計チームが関与し、製造と設計を完全に統合する体制を構築する。

主要プレイヤーの動向:四者四様の戦い方

半導体を牽引する企業は、それぞれの強みを軸に独自の2nm戦略を展開しています。

- NVIDIA

圧倒的なソフトウェア資産を武器に、ソフト最適化と先端パッケージを組み合わせ、AIインフラの主導権を握る。 - Apple

自社設計の強みを活かし、アーキテクチャ・EDA・DTCOを高度に統合した垂直モデルを追求する。 - AMD

先駆的なチップレット戦略をさらに進化させ、異なるノードのダイを柔軟に組み合わせる設計力を強化。 - TSMC

製造企業から脱却し、DTCOと3DFabricなどの先端パッケージを統合した“設計支援プラットフォーム”を提供する。

これらの企業に共通するのは、2nmを単なる微細化の延長ではなく、設計手法を根底から作り直す転換点と捉えていることです。

勝者は、技術そのものではなく、エコシステム全体をどう統合するかで決まります。

まとめ

2nmは、半導体の歴史において“設計”が主役へと完全に移行する転換点です。

本コラムで触れたように、アーキテクチャ、DTCO、パッケージ、EDA、検証が複雑に絡み合うこの領域では、単なる技術知識だけでは前に進めません。

だからこそ、今求められるのは、変化を恐れず新しい設計手法に挑む姿勢です。

2nmは難しい。

しかし、その壁を越えた先には、2030年代のAI社会を支える新しい半導体像が広がっています。

読者の皆さまが、この大きな変化を自らの成長の機会として捉え、次の一歩を踏み出すきっかけとなれば幸いです。