なぜ「次世代パッケージ」が注目されるのか

半導体の進化は「微細化」によって牽引されてきました。

トランジスタをより小さく高密度に集積することで、性能向上と省電力化を実現してきたのです。

しかし数ナノメートル世代に至り、微細化の効果は物理・経済両面で限界に近づき、製造コストは急増。熱や信号遅延などの課題も深刻化しています。

そこで注目されているのが「次世代半導体パッケージ」です。

従来は「完成チップを基板に実装する後工程」でしたが、今やシステム性能を左右する重要技術となっています。

本記事では、日本の新たな取り組み「JOINT3」の設立概要をはじめ、海外動向、市場性、技術課題までを解説します。

「JOINT3」設立の背景と意義

JOINT3(Resonac 主導)は「515 × 510 mm のパネル級有機インターポーザ(panel-level organic interposer)」を共同で開発する産業コンソーシアムです。

評価用の試作ライン(APLIC)を日本に作り、材料/装置/設計ツールを実運用に近い形で検証する方式がとられています。

運用は2026年開始予定で進んでいます。

海外の動向(先端パッケージ開発)

海外の取り組みは地域によってスタイルが異なっています。

台湾・韓国は“産業(OSAT/Foundry)主導で大規模な実機パイロットや量産投資”を進め、

欧州は研究機関(Imec、Fraunhofer 等)中心に技術課題の解決と標準化を狙い、

米国は政府資金(CHIPSプログラム等)を使った設備誘致と産学連携の拠点づくりで後工程強化が進められています。

台湾・韓国(産業・OSAT/Foundry 主導)

TSMC を筆頭に、OSAT(ASE など)や基板/材料メーカーがパネル級ラインの早期、検証・導入を進め、実用化・量産への動きが活発となっています。

ASE(Advanced Semiconductor Engineering) や台湾サプライチェーンはパネルでの実証を進めています。

現在の活動は?

- TSMC、Samsung など大手 Foundryが中心となり、最先端の2.5D/3D実装やハイブリッドボンディングの強化を進めています。

- ASE、SPIL(Siliconware Precision Industries Co., Ltd./品精密工業) などの OSAT企業も参入し、パネルレベルパッケージ(PLP)や大面積ファンアウトの量産検証を進めています。

将来の方向性

- 「高密度・低コスト・量産性」の3本柱。

- AI、サーバー、モバイル機器などで急増する需要を満たすため、600mm級パネル対応やガラスインターポーザなども視野に入れています。

- 台湾・韓国は「世界の製造ハブ」として、実際に市場に供給できる立場を維持する見込みのようです。

米国(政府主導+産学連携で戦略的整備)

CHIPS 法など公的資金で“後工程拠点”を誘致・育成:Amkor、GlobalFoundries、その他企業への補助/助成(あるいは研究拠点設置支援)が行われ、大型の先進パッケージング工場やR&Dセンターの整備が進んでいます。

現在の活動は?

- CHIPS法を通じ、先進パッケージング工場の誘致や研究拠点の整備に巨額投資がされています。

- Amkor、Intel、GlobalFoundries など企業が拠点を構え、大学(MIT、Georgia Tech など)や国立研究所も共同研究を進めています。

- 「設計力はあるが後工程は海外依存」という弱みの克服を進めています。

将来の方向性

- 米国は「技術リーダーシップ+国内供給網確保」が目的。

- 先進パッケージング+システム設計を組み合わせて、EDA(設計ツール)から実装まで一貫した強みを構築する方針。

- 政府支援により、国内エコシステム(大学、企業、スタートアップ)が強固につながる。

欧州(研究機関+産業連携で基礎+信頼性課題を解決)

Imec、Fraunhofer 等の公的研究機関が技術開発と信頼性評価を牽引しています。

高密度配線、ハイブリッドボンディング、熱管理や信頼性試験法など、産業化に先立つ“解決すべき技術課題”に注力し、企業との共同プロジェクトやイベント(Electronic Packaging Days 等)で知見を共有しています。

現在の活動は?

- Imec(ベルギー)、Fraunhofer(ドイツ)といった研究機関が中心で取り組んでます。

- 企業(ASML、STMicroelectronics、Infineon など)と連携し、材料・信頼性・熱管理・接合技術の基盤開発を行っています。

- 実用化というより、「業界共通課題を先に解決する」研究に重点が置かれているようです。

将来の方向性

- 「持続可能性(環境負荷低減)+信頼性(長寿命)」がキーワード。

- 自動車や産業機器など長寿命・高信頼分野で世界をリードする狙い。

- 欧州は量産力では劣るが、材料評価・標準化・品質保証で世界に影響を与える役割を担う。

次世代パッケージとは

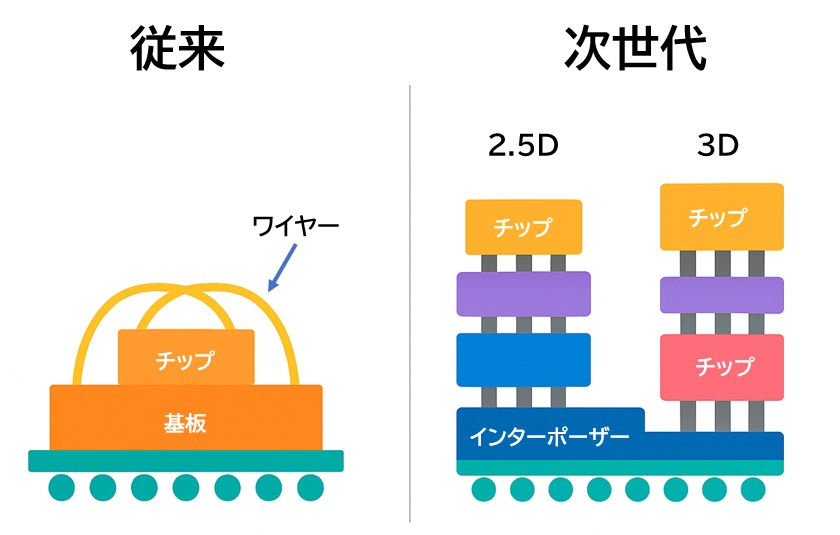

従来パッケージ

従来の半導体パッケージ技術では、完成したチップを基板上に配置し、ワイヤやバンプによって電気的に接続する方式が一般的でした。

この構造では、チップ間の配線距離が長くなり、信号の遅延や消費電力の増加といった課題が生じています。

また、設計の基本は単一チップを中心とした構成であり、システム全体の柔軟性や拡張性には限界がありました。

次世代パッケージ

次世代半導体パッケージは、微細化の限界に直面する中で、性能と柔軟性を両立する重要技術が注目されています。

代表的な技術の一つが「2.5Dパッケージ」で、インターポーザと呼ばれる中間基板を用いて複数チップを高密度に接続します。

さらに「3Dパッケージ」では、チップを垂直方向に積層し、TSV(シリコン貫通ビア)やハイブリッドボンディングによって接続することで、さらなる集積度と高速化を可能にします。

「ファンアウトパッケージ」は基板を使わず、再配線層によってチップを囲む構造を採用し、小型化と高性能化を両立します。

また、複数のチップを「チップレット」として組み合わせることで、用途に応じた柔軟なシステム設計が可能となり、製品開発の自由度が大きく広がります。

これらの技術は、微細化だけでは達成できない性能向上を補完するキーテクノロジーとして、今後の半導体開発において不可欠な技術となっています。

従来 vs 次世代パッケージ 比較表

| 項目 | 従来パッケージ | 次世代パッケージ |

| 接続方式 | ワイヤボンディング、バンプ接続 | 2.5Dインターポーザ、3D積層、ハイブリッドボンディング |

| 配線距離 | 長い → 遅延・消費電力大 | 極短 → 高速・低消費電力 |

| 構成 | 単一チップ中心 | 複数チップ(チップレット)集積 |

| 小型化 | 基板サイズに依存 | ファンアウトで基板レス・高密度化 |

| 技術目的 | 微細化を前提とした延長 | 微細化限界を補完し性能拡張 |

市場性と市場規模

記載されている市場規模の数値は、各種レポートからの引用に基づいています。

あくまでボリューム感の目安としてご参照いただき、金額は参考値として取り扱ってください。

市場全体のイメージ

グローバル市場における半導体パッケージング全体の規模は、2024年時点でおおよそ45〜50億ドル(約6〜8兆円)と推定されています(複数のレポートより)。

今後は先進パッケージの構成比が増加し、2030年には70〜110億ドル規模へと拡大する見込みといわれています。

先進パッケージ(Advanced Packaging:ファンアウト、FO-WLP、2.5D/3D、PLP、シリコン/ガラスインターポーザなど)の市場規模は、2024〜2025年にかけて約15〜30億ドルと推定され、用途の拡大や技術の多様化により、今後も成長が期待されています。

要素別市場規模

素材・材料(エポキシ樹脂、接着剤、導電ペースト、銅めっき材料、シリコン/ガラス基板材料 など)

2025年時点における半導体パッケージ材料の市場規模は、約200億〜260億ドルと推定されています。

特に、先進パッケージ向けの材料需要が急速に拡大しており、低CTE(熱膨張係数)フィルム、高導熱樹脂、ウエルド材料、バンプ材などが注目されています。

これらの材料には、高い信頼性や優れた熱特性、微細配線への対応力が求められ、性能要件を満たすことで製品の差別化が可能となり、価格面でもプレミアムが付く傾向があります。

特にAIや高性能コンピューティング用途では、高導熱かつ低応力の材料に対するニーズが今後さらに高まると見込まれています。

基板/サブストレート(半導体パッケージ基板)

2024年の報告によると、半導体パッケージに用いられるサブストレート(高密度サブストレート、ABF、コア基板など)の市場規模は約160億ドルと推定されています。

先進パッケージの普及に伴い、サブストレートの重要性はますます高く、今後も成長が見込まれています。

技術面では、高層配線構造や微細配線への対応、低誘電率材料の採用が競争の中心となっています。

これらの要素は、高性能・高密度なパッケージ設計を支える基盤技術であり、製品の差別化や信号伝送効率の向上に直結します。

また、サブストレートの量産には大規模な設備投資が必要であり、製造技術と資本力の両面が求められます。

この分野では、台湾、日本、韓国の企業が高い技術力と生産能力を有しており、グローバル市場において優位なポジションを築いています。

パッケージ(アセンブリ/組立・テスト・OSAT サービス)

半導体パッケージング市場において、パッケージングサービスは全体の中でも非常に大きな割合を占めています。

特に近年では、先進パッケージ技術の需要が急速に高まり、ファンアウト、2.5D/3D構造、ハイブリッドボンディングなどの高度な実装技術が市場成長を引き上げています。

これらの技術は、微細化の限界を補いながら、高性能・高密度なシステム構築を可能にするため、AIや高性能コンピューティングなどの分野を中心に採用が拡大しています。

今後も、パッケージングサービスは技術革新とともに市場規模を拡大し、半導体産業全体の競争力を左右する重要な要素となると見込まれています。

製造装置(組立・接合・検査・テスト装置)

半導体の後工程に用いられる製造装置(組立・接合・検査・テスト装置)の市場規模は、2024〜2025年にかけて約40億〜90億ドルと示唆されています。

この領域は、パッケージングの品質や歩留まりに直結するため、技術革新と設備投資の両面で注目されています。

特に、後工程では自動化の高度化が重要なテーマであり、リールやパネル処理に対応した装置、ハイブリッドボンディング技術を搭載した接合装置、そして微細構造を高精度に検査できる装置などが鍵を握ります。

これらの装置は高付加価値であり、導入には大規模な設備投資が必要なため、技術力と資本力を兼ね備えた企業が競争優位を築いています。

今後、先進パッケージの普及に伴い、製造装置の性能要求はさらに高まり、市場の成長とともに装置開発の重要性も増していくと考えられます。

パネルレベル(PLP)/新フォーマット(将来性の高いニッチ)

パネルレベルパッケージ(PLP)は、従来のウェハ単位の処理からパネルサイズへの拡張を図ることで、生産効率とコスト競争力を高める新しいパッケージング手法です。

いくつかの市場調査によれば、PLP関連市場は2030年までに数十億ドル規模に達する可能性があるとも予測されており、将来性の高いニッチ分野として注目されています。

この技術の導入初期には、設備構築や製造ラインの確立、歩留まりの安定化といった課題が存在します。

しかし、量産体制が整えば、従来のウェハレベルパッケージに比べて大幅なコスト削減が可能となり、特に高性能・高密度な実装が求められる分野での採用が期待されています。

なぜ市場が伸びるのか

- AI/データセンター向け高性能チップの増加:多ダイ搭載・高帯域幅メモリ(HBM)などが先進パッケージ需要を加速。

- モバイル/車載/IoTの多様なパッケージ要件:薄型化・信頼性(自動車)で新材料や高信頼パッケージが必要。

- パネル/PLP 等の新プロセスでコスト優位が期待:うまく量産に移れば単位コスト低減・歩留まり向上が可能。

- 国家戦略(米CHIPS 等)・投資動機:設備投資やサプライチェーン回帰が装置・材料需要を押し上げる。

最重要工程と装置 (技術難易度)

次世代半導体パッケージ(先端パッケージング:2.5D、3D、Fan-Out、Chipletなど)において、製造装置で最も重要かつ技術難易度が高い工程は、大きく3つが想定されます。

ハイブリッドボンディング(Hybrid Bonding)装置

- チップ同士、またはチップとウェハを、電気的・機械的に低抵抗かつ高密度で接続する。

- 高い難易度の理由

- 数百ナノメートル以下の位置合わせ精度(アライメント)が必要

- 表面の平坦性(CMP仕上げ)や清浄度が厳しく求められる

- 同時に「電気的接続」と「機械的接合」を行うため、材料(Cu-Cu、酸化膜など)の表面制御が難しい

- 主な装置メーカー:

- 国内:東京エレクトロン(TEL)、キヤノン、芝浦メカトロニクス

- 海外:Applied Materials、EVG(オーストリア)

高精度アライメント&マウンター(Die Bonder / Chip Placer)

- 複数のチップ(Logic、HBM、I/Oダイなど)を極めて狭ピッチで正確に配置。

- 高い難易度の理由

- ChipletやHBMでは数十〜数百マイクロメートルピッチの接続が必要

- 熱膨張によるズレをリアルタイム補正する高度な制御が必須

- 主な的装置メーカー:

- ASMPT(香港)、BESI(オランダ)、新川(日本)、K&S(米)

再配線層形成(RDL: Redistribution Layer)装置

- ファンアウトや2.5Dパッケージで、I/Oを外部接続向けに配線し直す。

- 高い難易度も理由

- 微細パターン形成(1〜2µm以下)にフォトリソやめっき技術が必要

- 大面積(パネルレベル)で均一性を保つ必要

- 樹脂・金属の膨張差による歪み制御

- 主な装置メーカー:

- リソ:Canon、Nikon、ASML(拡張応用)

- めっき:宇部マテリアルズ、Atotech(独)

まとめ

次世代半導体パッケージは、微細化の限界を超え、性能向上を支える重要技術です。日本ではJOINT3による産学連携が進み、海外でも各国が強みを活かして開発を加速しています。

ハイブリッドボンディングやRDL形成などの工程は今後も進化し、市場はさらに拡大する見込みです。課題の克服こそが新たな価値を生み、技術者の成長機会にもつながります。

材料・装置・設計・工程など、多様な分野で専門性を活かし、未来の半導体産業に貢献していきましょう。