AI時代におけるメモリの重要性

AIやHPC(高性能計算)、さらに生成AIを含む大規模モデルの急速な普及により、半導体に求められる演算能力はかつてないほどに高まっています。

GPUやAIアクセラレータは卓越した演算性能を備えていますが、その真価を発揮するには、演算ユニットへ継続的かつ高速にデータを供給できるメモリの存在が不可欠です。

演算回路の高速化だけでは限界があり、メモリ帯域が不足すればシステム全体の性能はメモリ帯域によって制約されます。これが半導体設計における最大の障壁となります。

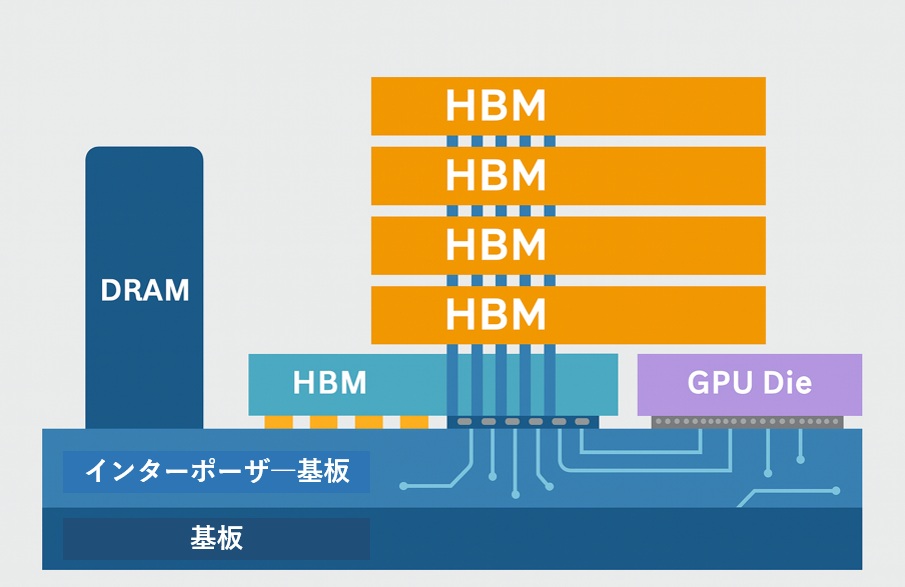

この課題への解決手段として登場したのが、HBM(High Bandwidth Memory)です。

3D積層技術によって広帯域を実現し、AIやHPC分野において不可欠な次世代メモリとして急速に発展しています。

本記事では、HBMの基本知識・特徴から、課題や導入事例、そして今後の市場展望を解説します。

HBMとは何か

半導体メモリは、電源供給でデータが消える揮発性メモリ(DRAM、SRAM)と、消えない不揮発性メモリ(フラッシュメモリ、ROMなど)に大別されます

HBM(High Bandwidth Memory)は、従来のDRAMを超える性能をもつ次世代のメモリ技術です。

メモリの種類と特徴

半導体におけるメモリは、「速度」と「容量」のトレードオフに基づいて階層的に構成されています。

以下は代表的なメモリの種類と特徴です。

| 分類 | メモリの種類 | 構造 | 主な用途 | 特徴 |

| 揮発性メモリ | DRAM (Dynamic RAM) | コンデンサ+トランジスタ | PCメインメモリ、サーバー、スマホ | 大容量・低コスト・リフレッシュ必要 |

| SRAM (Static RAM) | フリップフロップ回路 | CPUキャッシュ、ネットワーク機器 | 高速・高コスト・低密度・リフレッシュ不要 | |

| SDRAM (Synchronous DRAM) | DRAM+同期回路 | PC、モバイル | クロック同期で高速アクセス | |

| DDR SDRAM (DDR, DDR2, DDR3, DDR4, DDR5) | SDRAMの高速化 | PCメモリ、サーバー、GPU | データ転送速度向上、世代ごとに性能向上 | |

| LPDDR (Low Power DDR) | 低消費電力DRAM | スマホ、タブレット、モバイル機器 | 低消費電力・バッテリー駆動向け | |

| GDDR (Graphics DDR) | GPU用DRAM | グラフィックスカード、ゲーム機 | 高帯域幅・GPU専用 | |

| HBM (High Bandwidth Memory) | TSV積層型DRAM | 高性能GPU、AIチップ、HPC | 高帯域幅・低消費電力・3D積層 | |

| 不揮発性メモリ | MRAM (Magnetoresistive RAM) | 磁気トンネル接合(MTJ) | キャッシュ、IoT、産業機器 | 不揮発性・高速・耐久性高 |

| FRAM (Ferroelectric RAM) | 強誘電体 | POS端末、メーター、制御機器 | 不揮発性・高速・書き換え耐性高 | |

| ReRAM / RRAM (Resistive RAM) | 抵抗変化型 | IoT、AI、組み込み機器 | 不揮発性・高密度・低消費電力 | |

| EPROM (Erasable PROM) | 紫外線消去型 | ファームウェア、開発用 | 書き換え可能だが紫外線消去必要 | |

| EEPROM (Electrically Erasable PROM) | 電気消去型 | BIOS、設定情報保存 | 書き換え容易・容量小 | |

| Flashメモリ (NAND / NOR) | 電荷トラップ型 | SSD、USB、スマホ、デジカメ | 大容量・低コスト・ブロック単位で書き換え |

HBMの主な技術的特徴

HBMは、以下のような特徴を持ちます

- 3D積層構造:複数のDRAMダイを垂直に積層し、TSV(シリコン貫通電極)によって高速に接続します。

- 広幅I/O:動作クロックを過度に上げることなく、1,024bit以上の超広幅バスによって高スループットを実現します。

- 高帯域:HBM3では1,000GB/sを超える帯域を達成しており、従来のGDDR6の2倍以上の性能があります。

- 省電力:高クロック動作を避けることで、消費電力あたりの効率が高くなります。

HBMは世代ごとに「高速化・大容量化・低消費電力化」が向上し進化を続けています。

- HBM2 → HBM2E → HBM3 → HBM3E(2025年現在)

- HBM4は2030年前後の登場が見込まれており、さらなる帯域拡大が期待されています。

HBMの主な課題

HBMはAIやHPC分野において高い性能を発揮する一方で、導入・運用にはいくつかの技術的・経済的な課題があります。

特に製造コストや供給体制、熱設計など、実装時に考慮すべき課題が複数存在します。

(1) 高コスト

HBMは3D積層構造とシリコンインターポーザの実装が必要なため、DDRやGDDRと比較して製造コストが大幅に高くなります。

(2) 歩留まりの低下

積層されたDRAMダイのうち、1層でも欠陥があると全体が不良品となるため、特に8層以上の構成では製造難易度が高く、歩留まりが低下しやすいです。

(3) 供給制約

HBMを量産できるメーカーはSK hynix、Samsung、Micronの3社に限られており、急激な需要量の際に供給不足や価格高騰のリスクが潜在しています。

(4) 熱設計の難しさ

積層構造により発熱が集中しやすく、冷却技術の高度化が不可欠です。

特に高密度なGPUと組み合わせる場合には、熱設計がシステム全体の安定性に直結します。

課題解決への取り組み事例

これらHBMの課題に対して、改善及び研究開発が進められています。

主な改善・研究開発事例を紹介します。

既存メーカーによる改善事例(2022〜2025年)

- SK hynix:HBM3Eにおいて新たな検査手法を導入し、歩留まりの向上を実現しました。これにより、急増するAI需要への対応力を高めています。

- Samsung: FO-PLP (Fan-Out Panel Level Packaging)技術を応用し、製造工程の簡素化による低コスト化を模索しています。

- Micron:2024年にHBM3Eの量産を開始し、低消費電力化と大容量化の両立に注力しています。

- 冷却技術:液冷やマイクロ流体冷却の組み合わせにより、積層構造特有の発熱問題への対策が進められています。

2030年前後をめどに進行中の研究開発

- HBM with Hybrid Bonding:TSVに代わるハイブリッドボンディング技術により、接続密度の向上と歩留まり改善を目指しています。2030年頃の量産適用が期待されています。

- 光インターコネクトHBM:シリコンフォトニクスを活用し、GPUとの接続を電気から光へ転換することで、さらなる帯域拡大と低消費電力化を図っています。

- 冷却一体型HBM(液冷統合パッケージ):ダイ積層間にマイクロ流路を内蔵し、直接液冷を行うことで、発熱問題の根本的な解決を目指す研究が進行中です。

- 大容量HBM(32GB/stack超):積層数を16層以上に拡大する試みが進められており、歩留まりの課題は依然として大きいものの、AIの大規模モデル需要に応えるための重要技術とされています。

今後の可能性と市場性

HBMは技術的な進化とともに、AI・HPC分野における需要の高まりを背景に、今後も市場拡大が期待されています。

とくに生成AIの普及や大規模モデルの実用化が、HBMの価値をさらに押し上げる要因となっています。

- 市場規模予測

ある予測では、2025年時点では数十億ドル規模の市場が形成されると見込まれており、2030年にはその数倍に拡大すると予測されています。

生成AIの急速な普及が、HBMの需要を牽引する主要因となっています。 - HBM4への期待

次世代HBM4では、帯域幅がさらに2倍に拡張される見込みです。

また、冷却技術との融合による熱設計の最適化や、Hybrid Bonding技術の実用化によって、歩留まり改善と高密度実装が可能になると期待されています。 - 他メモリとの競合・共存

ReRAMやMRAMなどの新型不揮発性メモリが一部用途でHBMと競合する可能性がありますが、HBMはAIやHPCのような高帯域・高性能を要求される領域において、中核メモリとして長期的な優位性を維持すると見られています。

このように、HBMは技術革新と市場ニーズの両面から成長が加速しており、今後の半導体メモリ戦略において重要な位置を占めることになるでしょう。

まとめ

HBMは、AI半導体の性能を最大限に引き出すために欠かせない次世代メモリです。

しかし、コストや歩留まり、熱設計、供給制約といった技術的な課題も存在します。

これらの課題に対して改善や新技術の開発が進むことで新たなビジネスへの展開も予想されます。

この記事は、将来のエンジニアへ役立てばと思います。