生成AIの急速な普及により、AIデータセンターの電力消費は急激に増加しています。

前回のコラムでは、AIチップの競争軸が「配線密度」へ移行していることを解説しました。

しかし、その高密度な配線構造を実際に動かすためには、これまでにない規模の電力供給が必要になります。

いま現場で問題となっているのは、単純な「消費電力量の合計」だけではありません。

本当のボトルネックは「電力密度」にあります。

※電力密度とは、限られた空間にどれだけの電力を供給できるかという指標です。

以下は、要素の制約(例)となります。

- 1ラックあたりの電力供給の上限

- IRドロップ(配線抵抗による電圧降下)

- 電源プレーン(基板内の電源供給層)の設計

本コラムは連載の第2回です。

・第1回:AIチップの2nm競争は“配線密度”で決まる ― HBM・RDL・BSPDNが変える半導体構造

AIデータセンターにおける電源設計と電力密度の制約

従来のデータセンターでは、1ラックあたり数kWから10kW程度の電力が一般的でした。

しかし現在、GPUを複数搭載した最新のAIサーバーは、1台だけで数kW級の電力を消費します。

これを高密度にラックへ搭載すると、1ラックあたりの電力は数十kW規模にまで増加します。

つまり、AIデータセンターでは、従来とは桁違いの電力を限られた空間に供給しなければならないのです。

ここで重要になるのは、「平均消費電力」ではありません。

本当に問題になるのは「瞬間的な電力密度」です。

AIの処理(AIワークロード)は負荷の変動が非常に激しく、ミリ秒(1000分の1秒)単位で電流が急増します。

その結果、次のような現象が起こります。

- 電源の応答が追いつかない

- 電圧が一時的に低下する(電圧降下)

- 計算エラーが発生する

- システム全体の処理性能(スループット)が低下する

つまり、問題は「どれだけ電力を使うか」ではなく、

「どれだけ急激な電流変化に耐えられるか」に移っているのです。

この変化により、データセンターの設計思想は変わりました。

これまでは「発生した熱をどう逃がすか」という熱設計が中心でした。

しかし現在は、「大電流をいかに安定して供給するか」という電流設計がより重要になっています。

GPU電力がAIデータセンターを決定する理由

現在のAIインフラを牽引しているのは、NVIDIAやAMDなどが開発する高性能GPUです。

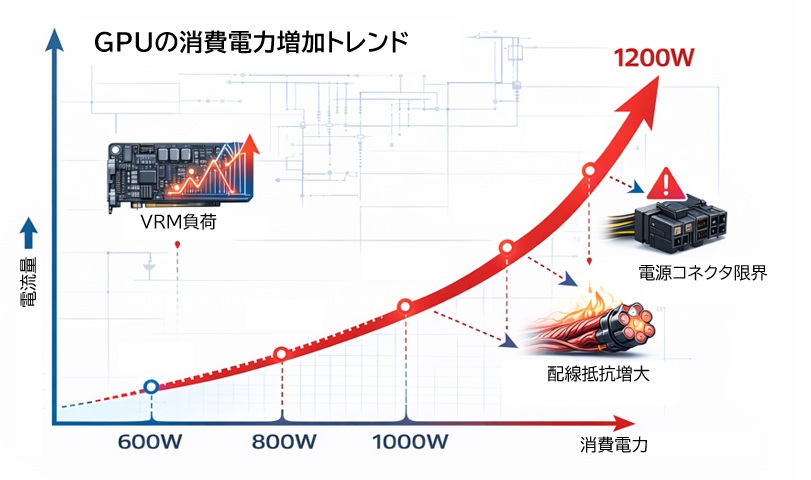

これらのGPUは、飛躍的な性能向上を実現する一方で、消費電力も年々増加しています。

データセンターに実装する際に問題となるのは、単なる「性能/ワット(電力効率)」だけではありません。

実際の現場では、次のような物理的な制約が支配的になります。

- 1ボードあたりの最大電流の増大

- 電源コネクタの容量限界(流せる電流の上限)

- VRM(電圧レギュレータ:電圧を安定させる回路)の高密度化と発熱

- 配線抵抗による電力損失の増加

GPUの消費電力は、800W、1000W、そして1200Wへと拡大しつつあります。

この水準になると、もはや単純な冷却強化だけでは対応できません。

ラック設計の本質は、「発生した熱をどう処理するか」という熱設計から、

「大電流をいかに安定して供給するか」という電流設計へと移行しています。

つまり、GPUの進化は、データセンター全体の電源インフラの再設計を迫っているのです。

2nm消費電力の現実 ― BSPDNは救世主となるか

次世代の2nmプロセスでは、トランジスタ1個あたりの効率改善が期待されています。

理論上は、同じ性能なら消費電力を下げることが可能です。

しかし実際には、AIチップはトランジスタ数そのものも急増させています。

そのため、チップ全体としての総消費電力は横ばい、あるいは増加傾向にあります。

さらに問題となるのは、

- ピーク電流の増大

- 電源ノイズの増幅

といった「電流の質」の問題です。

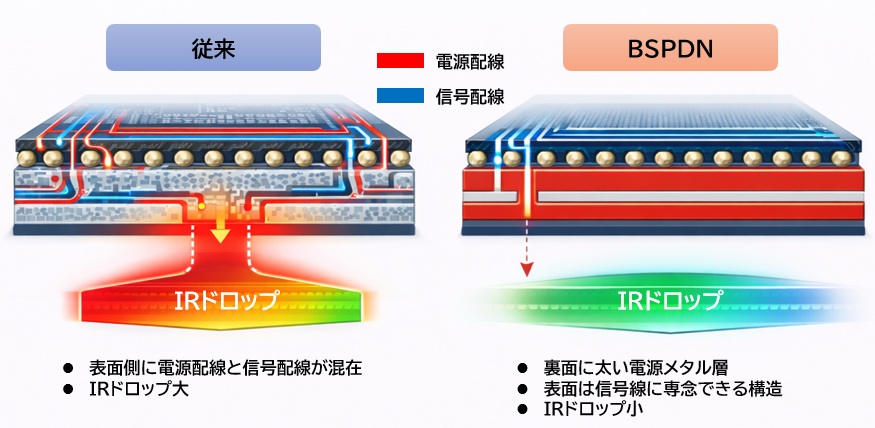

この課題に対して導入が進んでいるのが、

BSPDN(Backside Power Delivery Network:裏面電源供給ネットワーク)です。

従来は、チップの表面側から電源を供給していました。

しかしBSPDNでは、チップの裏面から直接電力を供給します。

その結果、次のような改善が期待できます。

- 電源配線の抵抗を大幅に低減

- IRドロップ(配線抵抗による電圧低下)の抑制

- 表面配線を信号線に集中させることが可能

つまり、チップ内部の電力供給効率を根本から改善する技術といえます。

■給電比較表

| 項目 | 従来の給電構造 | 2nm以降のBSPDN |

| 給電経路 | チップ表面から供給 | チップ裏面から直接供給 |

| IRドロップ | 大(配線抵抗の影響を受けやすい) | ◎ 極めて小さい |

| 配線密度 | 信号線と電源線が混雑 | ◎ 表面を信号線に特化できる |

ただし、BSPDNは「チップ内部」の問題を解決する技術です。

しかし、それだけでは不十分です。

真価を発揮させるためには、以下の外部設計も同時に最適化する必要があります。

- パッケージ基板の電源層設計

- PCB(プリント基板)の電源プレーン構造

- VRMの応答速度

- ラックレベルでの電源供給能力

つまり、チップ・パッケージ・基板・ラックまでを含めた統合的な電源設計が不可欠なのです。

実装技術の核心(IRドロップと電源プレーン)

AIチップのような超高密度回路では、大電流が局所的に集中します。

その結果、配線抵抗によって電圧が低下する現象が発生します。

これが「IRドロップ」です。

IRドロップが大きくなると、

- 信号のタイミング余裕(タイミングマージン)が減少

- 動作不安定

- 計算エラーの増加

といった問題が起こります。

もはや電源設計は、単なる回路設計ではありません。

構造そのものを最適化する「実装技術」の領域へと広がっています。

具体的には、

- 銅厚を増やして抵抗を下げる

- リターンパス(電流の戻り経路)を確保する

- デカップリングキャパシタを最適配置する

- フェーズ分割により電流負荷を分散する

といった対策が重要になります。

| 対策 | 目的 | 効果 |

| 銅厚の増加 | 抵抗低減 | IRドロップ抑制 |

| リターンパス確保 | 電流経路の安定化 | ノイズ低減 |

| デカップリング配置 | 瞬間電流の吸収 | 電圧変動の緩和 |

| フェーズ分割 | 電流負荷の分散 | VRM安定性向上 |

特にデカップリングキャパシタは、ミリ秒以下の急激な電流変動を吸収する

「瞬間的な電力バッファ」として機能します。

AIワークロードの安定動作は、この見えない部分の設計品質に大きく依存しているのです。

まとめ ― 勝敗を分けるのは“電力密度設計力”

AIデータセンターの拡張を制約するのは、需要でも半導体の微細化でもありません。

限られた空間にどれだけ安定した電力を供給できるかという、物理的な上限です。

電力密度への対応力は、単なる設計課題ではなく、競争優位そのものになりつつあります。

今後の勝敗を分けるのは、

高性能チップを作れる企業ではなく、それを支える電力アーキテクチャを構築できる企業です。

AIインフラ競争は、すでに“電力設計力”の時代に入っています。