はじめに

半導体は、長く性能向上を支えてきた“微細化”は物理的にも経済的にも限界が見え始めました。

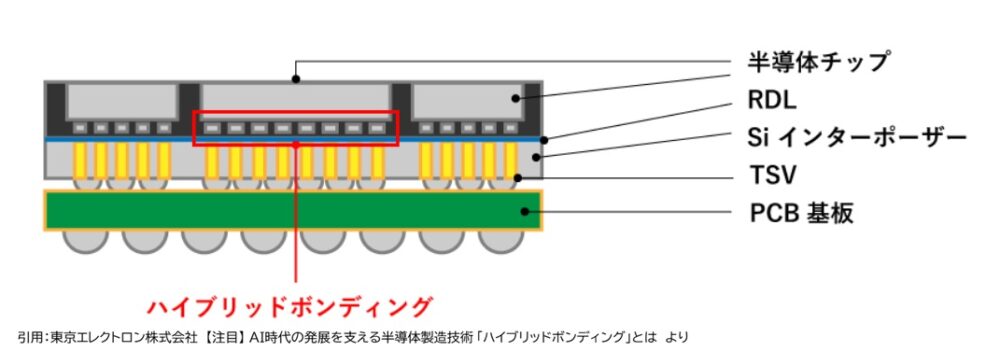

そこで注目されているのが、チップを横ではなく「縦」に積む3D積層技術、そしてその中核となる技術の一つが「ハイブリッド接合(Hybrid Bonding)」です。

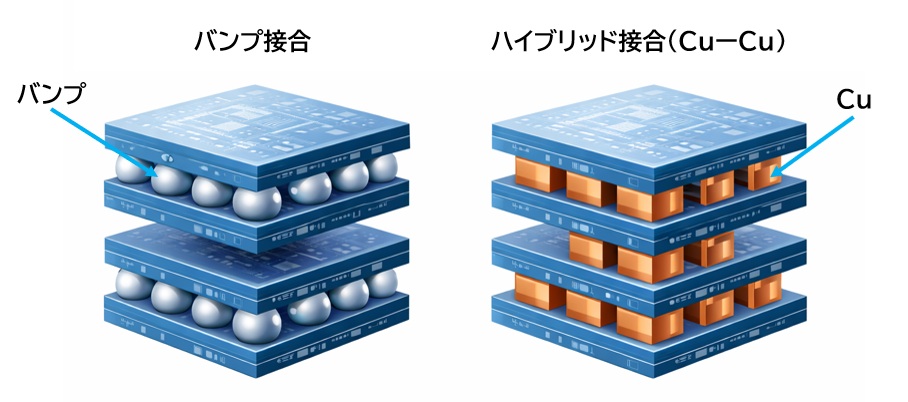

従来の積層では、チップ同士をつなぐために小さなハンダ(バンプ)を使っていました。

しかし、このバンプが占有面積・電気抵抗・発熱の面で大きな障害となっています。

ハイブリッド接合は、このハンダを使わず、鏡面のように平坦化したチップ同士を直接つなぐ接合方式です。

これにより、チップ間の距離は極限まで縮まり、境界そのものはほぼ消えてしまいます。

- 生成AIの高速化:膨大なデータを瞬時にやり取りでき、タイムラグが劇的に低減

- 電力効率の向上:配線抵抗によるロスが減り、データセンターの消費電力削減に直結

ハイブリッド接合により、パッケージングがチップ性能を左右する重要プロセスへと変わりました。

本コラムでは、半導体の常識を塗り替えつつあるこの技術の仕組みと可能性を、わかりやすく解説していきます。

従来の接合技術とハイブリッド接合の比較

半導体の多層化では、「バンプ(Bump)」と呼ばれる金属突起を使った接続が主流です。

しかし、ハイブリッド接合によって、接続は“点”から“面”へとなり、性能が大きく向上しています。

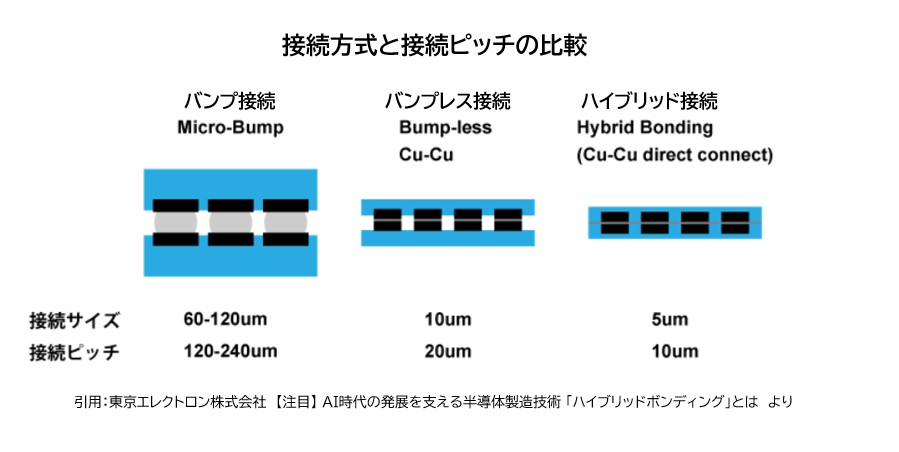

接続密度の飛躍(ピッチの微細化)

従来のバンプ接合では、ハンダ同士のショートを避けるため、バンプ間に一定の距離が必要でした。

- マイクロバンプ:240〜120μmピッチ。1mm²あたり数千〜数万接続が上限。

- ハイブリッド接合:ハンダを使わず、銅電極を絶縁層に埋め込む構造のため、10μm以下まで微細化可能。

配線層の厚み削減と電気特性の改善

バンプ接合では、ハンダの高さ(10〜30μm)がそのままチップ間の“隙間”となり、電気的ロスの原因となります。

従来方式の課題

- ハンダは銅より抵抗が高い

- バンプ形状の変化によって電気的なつながりが不連続になり、信号が乱れやすい

ハイブリッド接合の強み

- 接合厚みはほぼゼロ

- 銅同士が原子レベルで一体化し、抵抗・余分な電気的容量が大幅に低減→ 高周波信号をクリーンに伝送でき、データ1ビットを送るためのエネルギーが大幅に低減します。

放熱性と信頼性の向上

3D積層で避けて通れないのが「熱」の問題です。

バンプ方式の弱点

- チップ間の隙間に充填する樹脂(アンダーフィル)は熱を通しにくく、内部に熱がこもりやすい

ハイブリッド接合の利点

- チップ全面が銅と絶縁膜で密着し、垂直方向の熱伝導が高い→ 高密度な演算を行うチップを積層しても、効率よく熱を逃がせます。

■ マイクロバンプ接続/ハイブリッド接合バンプレス(Cu‑Cu)/ハイブリッド接合(Cu直接接合)の比較表

| 項目 | ハイブリッド接合(Cu直接接合) | ハイブリッド接合バンプレス(Cu‑Cu) | マイクロバンプ接続 |

| 接続方式 | 銅同士を直接接合する「面」接続 | 銅と絶縁体による「面」接合 | ハンダによる「点」接続 |

| 接続ピッチ | 10µm以下(さらに微細化可能) | 20 µm以下 | 120〜240 µm |

| インターコネクト厚 | ほぼ0 µm(原子レベルで一体化) | ほぼ0 µm | 10〜30 µm |

| 主な抵抗要因 | 接合界面の抵抗が極めて小さい | ほぼ無視できるレベル | ハンダ抵抗・不要な容量 |

| 放熱経路 | 銅同士が直接つながり熱伝導が最も良い | チップ全体で熱を伝導 | 樹脂が熱を遮断しやすい |

| 特徴 | 最低抵抗・最高密度・高信頼性 | 高密度・低抵抗・高周波に強い | 実装容易・既存技術と互換性 |

ハイブリッド接合を実現する「3つの技術的ブレイクスルー」

ハイブリッド接合は構造としてはシンプルですが、量産化には従来のパッケージ技術を大きく超える精度が必要です。

その実現を支えているのが、後工程に“前工程レベル”の精密さを持ち込んだ3つの技術革新です。

超精密平坦化(ナノレベルCMP)

ハイブリッド接合では、接合面が“鏡以上”に平坦でなければなりません。

そのために使われるのが化学的機械研磨(CMP)です。

- ナノレベルの凹凸管理

表面に数ナノメートルの凹凸があるだけでボイド(空隙)が発生し、接合不良につながります。

- ディッシング対策

銅(Cu)は柔らかく、絶縁膜(SiO₂)は硬いため、同時に研磨すると銅が中央だけ凹む「ディッシング(Dishing)」が起こります。

(ディッシング(Dishing):CMPで研磨する際、配線部分が周囲の絶縁膜よりも過剰に削られ、中央が“くぼむ”ように凹む現象)

ハイブリッド接合では、銅をあえて数ナノメートル低く残し、後の加熱で膨張させることで上下電極をぴったり密着させる高度な制御が行われています。

表面活性化による常温接合

ハンダも接着剤も使わずに“置くだけでくっつく”理由は、表面活性化技術にあります。

- 親水性による自発接合

プラズマ処理で表面に水酸基(–OH)を形成すると、ウエハー同士が水素結合で常温でも吸い付くように仮接合します。

- Cu-Cu拡散による本接合

その後200〜400℃の低温アニールで銅原子が拡散し、銅同士が金属結合、絶縁膜同士が共有結合を形成。結果として、電気的にも機械的にも“一体化した構造”が完成します。

サブミクロン精度のアライメント

接続ピッチが1μm以下になると、位置ずれは致命的です。

- ボンダの極限精度

従来のフリップチップボンダは数μm精度でしたが、ハイブリッド接合では数百nm以下の位置合わせが必須です。

- 光学+精密制御の融合

高解像度カメラで電極位置を認識し、ピエゾ素子などの微細アクチュエータで調整することで、ウエハー全面にある数千億の接続点を正確に重ね合わせる技術が確立されています。

製造プロセスにおける課題と克服すべき壁

ハイブリッド接合は半導体の性能ロードマップを大きく前進させる技術ですが、量産化には従来の後工程(OSAT)の枠を超える高度な管理が必要です。

パーティクル管理の“前工程化”

ハイブリッド接合の最大の歩留まり低下要因は、パーティクルです。

- 致命的なサイズ感の変化

バンプ接続では数十μmのハンダが多少の塵を包み込めましたが、ハイブリッド接合は面同士を分子レベルで密着させるため、数十nmの異物でも大きな未接合領域(ボイド)を生みます。

- クリーンルーム要求の再定義

その結果、パッケージ工程であっても露光工程並みのクラス1レベルの超クリーン環境が求められるようになりました。

KGD保証と積層リスク

(KGD保証: KGD(Known Good Die:既知良品ダイ)を確実に選別し、良品だけを積層やパッケージ工程に使うことを保証する仕組み のことです。)

積層数が増えるほど、1つの不良が製品全体の廃棄につながります。

- 複合歩留まりの落とし穴例

歩留まり90%のチップを10層積むと、最終歩留まりは35% に低下します

(各チップが独立して90%の確率で良品だとしても、1枚目が良品である確率:0.9、2枚目も良品である確率:0.9 × 0.9 ・・・・・・・・10枚すべて良品:0.9¹⁰) - 検査技術の限界

ハイブリッド接合は“剥がして修理”ができないため、接合前に完全性を保証するKGD選別と、ナノピッチでのプロービング技術が不可欠です。

D2Wプロセスのスループット問題

ハイブリッド接合には「W2W(ウエハー同士)」と「D2W(チップを個別に貼る)」の2方式があります。

- W2Wの制約

生産性は高いものの、以下のような歩留まり面の課題があります。

1.上下のチップサイズが同じである必要

2.不良チップもまとめて接合してしまう - D2Wの課題

良品だけを選んで貼れる柔軟性はあるものの、サブミクロン精度のアライメントをチップごとに実施するためスループットが低下します。

現在は、プラズマ処理〜洗浄〜配置〜接合までを高速かつクリーンに自動化する装置開発が競争の中心です。

CTEミスマッチとワーページ(反り)

異なる材料を積層する際、熱膨張率(CTE)の差が大きな問題になります。

- 熱応力による反り

アニール工程で材料が異なる膨張を起こし、ウエハーやチップが反ります。 - 界面剥離のリスク

ナノレベルで密着した接合界面に応力が集中し、剥離やクラックの原因に。

これを防ぐには、応力緩和材料の選定や加熱・冷却プロファイルの最適化が欠かせません。

この技術が「世の中」をどう変えるのか

ハイブリッド接合は、単なる製造プロセスの改良ではありません。

コンピューティングの限界を押し広げることで、社会インフラから日常生活まで幅広い領域に影響を与える技術です。

生成AIの「思考速度」と「精度」を大幅に引き上げる

現在の生成AIが抱える最大のボトルネックは、GPU性能ではなくメモリ帯域の不足です。

- リアルタイムAIの実現

ハイブリッド接合により、プロセッサとメモリ(HBM)が隙間なく直結され、データの往復時間が大幅に短縮されます。

その結果、医療診断・自動運転・高度翻訳など、リアルタイム性が求められる分野でAIが本来の性能を発揮できるようになります。

データセンターの電力問題を根本から改善

世界中のデータセンターの電力消費は急増しており、持続可能性が大きな課題です。

- 圧倒的な省電力化

バンプ接続では信号を“持ち上げる”ために多くの電力が必要でしたが、ハイブリッド接合は配線抵抗を極小化し、同じ処理をより少ないエネルギーで実行できます。

これは、ITインフラの省エネ化やカーボンニュートラル達成に向けた重要な技術となります。

チップレット化によるハードウェア開発の民主化

従来は巨大な一枚チップに全機能を詰め込む必要があり、開発コストも期間も膨大でした。

- 最適化デバイスの迅速な市場投入

チップレット技術が普及すれば、必要な機能だけを組み合わせてデバイスを構築できます。これにより、特定疾患向けの医療チップや、地域ニーズに合わせた低価格・高性能デバイスが短期間で開発可能になります。

エッジコンピューティングとスマート社会の加速

チップが薄型・低消費電力になることで、あらゆるモノに“知能”が組み込まれる世界が近づきます。

- 高機能ウェアラブル・XRの普及

小型ながらPC並みの処理能力を持つスマートグラス、補聴器、ヘルスケアデバイスが登場します。

クラウドに依存せず、その場で高度な処理を行うことで、プライバシーを守りながら人々の生活をより便利に、豊かに変えていきます。

まとめ:ハイブリッド接合が拓く「シリコンの新しい物語」

ハイブリッド接合は、半導体の進化を「平面の微細化」から「立体の高密度化」へと導き、計算能力の価値そのものを次の段階へ押し上げる静かな革命です。

日本には、この技術を支える精密装置メーカーやナノレベルの材料技術を持つ企業が数多く存在します。

技術者や学生がこの分野に挑むことは、優れた製品を生み出すだけでなく、AIと共に生きる未来社会の基盤を築くことにつながります。