AIの進化はGPU性能の向上によって加速してきました。

しかし現在は、GPUの性能にメモリが追いつかないことが大きな課題になっています。

特にHBMは高速ですが、積層数や配線構造に限界があり、これ以上の性能向上が難しくなりつつあります。

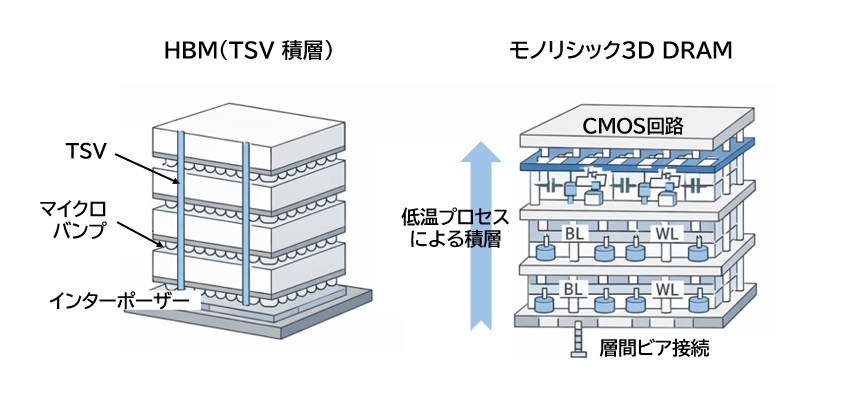

そこで次の候補として注目されているのが「モノリシック3D DRAM」です。

これは、メモリセルをチップ内部で縦に積み上げる新しい構造で、HBMでは突破できない帯域・容量・消費電力の壁を越えられる可能性があります。

ただし、製造工程の革新が必要で、量産化にはまだ課題が残っています。

本コラムでは、2026年時点の研究成果や企業ロードマップをもとに、 実現性・量産時期・有力企業・装置材料メーカーへの影響 といった観点から、モノリシック3D DRAMの全体像を簡潔に整理します。

関連記事:AIチップの2nm競争は“配線密度”で決まる― HBM・RDL・BSPDNが変える構造

モノリシック 3D DRAMは実現するのか

モノリシック3D DRAMは、2026年時点で「実現可能性は着実に高まっているものの、量産はまだ数年先」という段階にあります。

複数の企業や研究機関がプロトタイプの実証や基盤技術の論文発表を進めており、特に Samsung、 SK-hynix、 Kioxia、 Georgia Tech などが積極的に取り組んでいます。

一方で、DRAM特有の高速性・信号整合性・高サイクル耐性といった要求は非常に厳しく、3D NANDとは比較にならないほど高い技術ハードルが存在します。

そのため、研究レベルでは成果が蓄積されているものの、量産技術として確立するには依然として大きな課題が残っています。

| 項目 | 状況(2026年時点) |

| 技術的実現性 | 研究レベルでは実証が進み、プロトタイプ報告も複数存在 |

| 量産時期予測 | ・Samsung:2020年代後半 ・SK hynix:2030年頃 ・Kioxia:2030年代参入 |

| 主な課題 | ・高アスペクト比エッチング ・コンフォーマルALD ・配線遅延 ・信号整合性 ・Row Hammer耐性 |

| 市場背景 | ・AI需要による帯域幅 ・容量要求の急増で3D化は不可避 |

量産時期の見通し

モノリシック3D DRAMの量産時期については、2026年時点で複数の企業がロードマップを示しており、最速で2029〜2030年に初期製品が登場する可能性があります。

ただし、DRAM特有の信頼性要求や歩留まり確保の難しさを考えると、本格的な普及は2032〜2035年が現実的だと考えられます。

| フェーズ | 時期 | 内容 |

| 技術検証(PoC) | 2026〜2027年 | 研究機関や企業がプロトタイプを発表し、セル積層や低温プロセスの実証が進む段階です。 |

| 初期サンプル | 2028〜2029年 | SamsungやSK hynixが顧客向けに限定的なサンプル提供を開始する可能性があります。 |

| 量産開始 | 2029〜2031年 | HBMの一部構造をモノリシック化した初期製品が登場し、限定用途で採用が進むと見られます。 |

| 本格普及 | 2032〜2035年 | AI/HPC向けに本格採用が進み、HBMの後継技術として主流化するフェーズです。 |

最速で2029〜2030年に量産が始まる理由

モノリシック3D DRAMの量産化を後押しする技術要因として、以下の進展が挙げられます。

- ハイブリッドボンディング技術の成熟

HBM4以降で採用が進み、前工程への応用が現実味を帯びています。 - 高アスペクト比キャパシタ材料の進展

TiO₂系材料など、3Dキャパシタに適した高誘電率材料の研究が進んでいます。 - 低温プロセスの改善(BEOL CMOS)

酸化物半導体や低温ALDの進展により、上層CMOS形成の実現性が高まっています。

これらの技術が揃うことで、2029〜2030年に初期製品が登場する可能性が出てきています。

関連記事:2nm/16Aを制する極低温エッチングの衝撃ーALEの現場課題・製造装置

実用レベルでは2032〜2035年

一方で、DRAMは非常に厳しい信頼性要求を持つため、量産初期から高い歩留まりを確保することは容易ではありません。

- DRAMは10¹⁶回以上の書き換え耐性が必要

- Row Hammerやセル干渉など、積層による信頼性課題が増大

※Row Hammer : DRAM の特定の行(Row)を高速で繰り返しアクセスすると、隣接する行のデータが書き換わってしまう現象

※セル干渉 : DRAMセル同士が電気的に影響し合い、本来保持すべきデータが変化したり、読み書き動作に誤差が生じる現象 - GPUメーカー(NVIDIA/AMD)は数世代の検証を経て採用を決定する傾向

これらを踏まえると、モノリシック3D DRAMがAI/HPC向けの“主流メモリ”として広く採用されるのは、2032〜2035年が現実的なシナリオだと考えられます。

モノリシック3D DRAMは「ビジネスとして成立する」か

モノリシック3D DRAMは、単なる技術的な進化にとどまらず、メモリ産業全体の収益構造を大きく変える可能性を持っています。

HBMの需要が急拡大する中で、メモリメーカーは高付加価値製品へのシフトを強めていますが、HBMには構造的な限界があり、次のブレークスルーが求められています。

HBMの「限界」を突破する唯一の道

HBMは高帯域を実現する一方で、以下のような構造上の限界が顕在化しています。

- TSV本数の限界

- スタック数の限界(12〜16Hiが物理的上限)

- 配線遅延の増大

- パッケージ熱密度の限界

これらにより、HBMは「横方向の帯域」は増やせても、「縦方向の容量」を増やすことが難しくなっています。

モノリシック3D DRAMは、この構造的な限界を根本から解消します。

- 帯域:ビットラインが短くなり、レイテンシが改善

※ビットライン :DRAMセル(1T1C)のキャパシタに蓄えられた電荷を読み書きするための“縦方向の配線”のこと

※レイテンシ :データの要求から応答が返ってくるまでにかかる“遅延時間”のことです。 - 容量:セルアレイを縦方向に積層でき、容量密度が飛躍

※セルアレイ :DRAMセル(1T1C:トランジスタ+キャパシタ)が規則的に並んだ“メモリの本体部分”のこと - 消費電力:配線長が短縮され、大幅に削減

HBMの後継として最も合理的な進化方向であり、GPUメーカーが求める性能向上を満たします。

メモリメーカーの収益性が劇的に改善する

DRAMビジネスは、微細化の限界と設備投資の巨大化により、収益性が低下しやすい構造にあります。

- 微細化の限界

- 設備投資の増大

- ASP(平均販売価格)が上がりにくい

- Samsung / SK hynix / Micron の寡占による競争激化

モノリシック3D DRAMは、この構造を大きく変える可能性があります。

- 微細化依存 → 積層依存へシフト

- 容量あたりコストを大幅に低減

- 技術参入障壁が極端に高く、差別化が可能

- AI/HPC向けの高単価市場に直結

これは、NANDが2Dから3Dへ移行した際に起きた「収益革命」が、DRAMでも再現されることを意味します。

GPUメーカー(NVIDIA / AMD / Intel)にとっても必須

Rubin世代以降のGPUでは、HBM帯域が性能ボトルネックになりつつあります。

NVIDIAはすでに

- HBM4で 2 TB/s超

- HBM4Eで 3 TB/s超

といった帯域を要求しており、HBMの限界が明確になっています。

モノリシック3D DRAMは、GPUの性能向上に直結するメリットを持ちます。

- レイテンシ低減

- 帯域増加

- 容量増加

- 消費電力削減

もしNVIDIAが採用を決めれば、業界全体が一気にモノリシック3D DRAMへシフトする可能性があります。

ビジネスとして成立する可能性は極めて高い

技術的な難易度は非常に高いものの、

- HBMの限界

- AI/HPC市場の拡大

- メモリメーカーの収益改善ニーズ

- GPUメーカーの帯域要求の急増

といった複数の要因が重なり、モノリシック3D DRAMは「技術的にも、ビジネス的にも」成立する可能性が高いといえます。

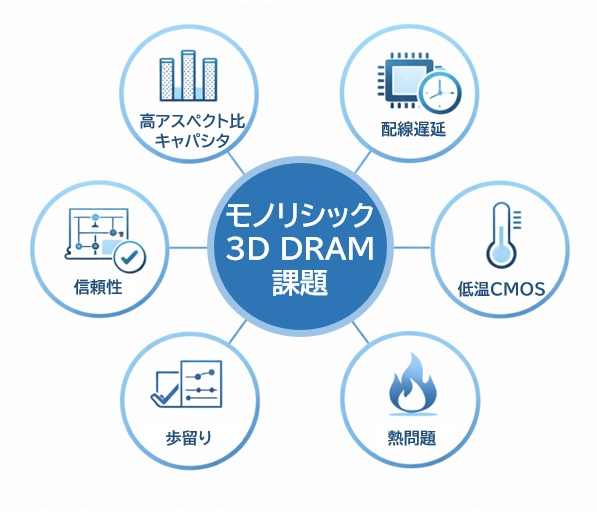

モノリシック3D DRAMの技術的な課題

モノリシック3D DRAMは、HBMの限界を突破する最有力技術として期待される一方で、実現には前工程の大幅な革新が必要です。

特に、DRAMは高速性・信号整合性・高サイクル耐性といった厳しい要求を持つため、3D NANDのように単純に「積めばよい」というものではありません。

モノリシック3D DRAMの課題5件

モノリシック3D DRAMは、「DRAMセルアレイ+周辺回路を同一ウェハ上で縦方向に積層する」 という構造を採用します。

このため、課題は以下の5つに分類できます。

1. DRAMセルの“縦積み”に伴う構造的課題

DRAMセルは1T1C構造であり、キャパシタの形状が3D化に向いていません。

※1T1C構造 :DRAMセルが “1つのトランジスタ(1T)+1つのキャパシタ(1C)” で構成される基本構造のこと

- キャパシタのアスペクト比が極端に高くなる

- 電極のコンフォーマル成膜が難しい(ALDの限界)

- キャパシタのリーク電流が増加

- セル間干渉(クロストーク)が増大

→ DRAMの本質である1T1C構造が3D化に不向きで、構造的な再設計が必要です。

2. ビットライン/ワードラインの配線遅延・抵抗増大

積層により配線が長くなることで、速度劣化が顕著になります。

- RC遅延が増加し、読み出し速度が低下

※RC遅延 :配線の抵抗(R)と容量(C)が原因で信号の立ち上がり・伝搬が遅くなる現象のこと - センスアンプの感度不足

※センスアンプ :DRAMセルから読み出される“極めて小さな電圧の差”を検出し、0/1 を判定するための増幅回路のことです。 - ノイズマージンの低下

→ DRAMは“速度が命”のため、遅延増加は致命的です。

3. 低温プロセスでの周辺回路形成(BEOL CMOS)

※低温プロセス :半導体製造で通常必要な高温(900〜1000℃)を使わず、 約400℃以下の温度で薄膜形成・アニール・トランジスタ作製を行う技術のこと

モノリシック3Dでは、下層の回路を壊さないように、上層を400℃以下の低温プロセスで作る必要があります。

しかし、DRAM周辺回路は高速CMOSが必要であり、本来は900〜1000℃級の高温アニールが不可欠です。

- 低温ではトランジスタ性能が大幅に劣化

- 酸化膜品質が低下し、信頼性が確保できない

- BEOL CMOS技術はまだ研究段階

※BEOL CMOS(Back-End-Of-Line CMOS) :通常は前工程(FEOL)で作るCMOSトランジスタを、 配線層(BEOL)側で低温プロセスを使って作る技術のことで

| 項目 | 通常のCMOS(FEOL) | BEOL CMOS |

| 作る場所 | トランジスタ層(基板上) | 配線層(BEOL) |

| 温度 | 900〜1000℃ | 400℃以下 |

| 性能 | 高速・高信頼性 | 低温のため性能が劣る |

| 用途 | CPU/GPU/DRAM周辺回路 | モノリシック3D DRAMの上層回路 |

→ “高速CMOSを低温で作る”という矛盾が最大の壁です。

4. 熱問題(Thermal Budget)

積層構造は熱がこもりやすく、DRAMセルの特性劣化を引き起こします。

- DRAMセルは熱に弱く、リーク電流が増加

- リフレッシュ回数が増え、消費電力が悪化

- GPUパッケージと組み合わせると熱密度がさらに上昇

→ HBM以上に熱設計が難しくなります。

5. 歩留まり・信頼性(Row Hammer、FBEなど)

積層によりセル干渉が増え、信頼性確保が難しくなります。

- Row Hammer耐性の低下

- Floating Body Effect(FBE)の顕在化

※Floating Body Effect(FBE) :トランジスタの“ボディ(基板部分)”が電気的に浮いた状態になること - 積層数が増えるほど歩留まりが指数関数的に悪化

→ DRAMは信頼性要求が極端に高いため、歩留まり確保が最大の難関です。

最大のボトルネックは何か?

最大のボトルネックは「低温プロセスで高速CMOSを作れないこと」 にあります。

- DRAMの速度は周辺回路(センスアンプ、プリチャージ、デコーダ)が決める

- しかし、上層CMOSは400℃以下で作る必要がある

- 高速CMOSは900〜1000℃の高温アニールが必須

- 低温ではトランジスタ性能・酸化膜品質が大幅に劣化

→ 現状のBEOL CMOS技術では、DRAMに必要な性能を満たせません。

この問題を解決しない限り、モノリシック3D DRAMの量産化は困難といえます。

モノリシック3D DRAM ・HBM・既存技術との比較

モノリシック3D DRAMを理解する上で、従来DRAM(2D)、HBM(3DスタックドDRAM)、そしてモノリシック3D DRAMの違いを理解します。

これら3つは「3D」という言葉が共通して使われるものの、構造・製造プロセス・性能特性は大きく異なります。

3つのDRAMアーキテクチャの違い

- 従来DRAM(DDR/GDDR)

→ 2D平面構造で、セルアレイと周辺回路を同一層に形成する最も一般的な方式です。 - HBM(3DスタックドDRAM)

→ 複数のDRAMダイをTSVで垂直に積層し、後工程で接続する方式です。帯域は高いものの、容量拡張には限界があります。 - モノリシック3D DRAM

→ セルアレイそのものを前工程で縦方向に積層する“真の3D構造”であり、HBMの限界を突破する可能性があります。

比較表

| 項目 | モノリシック3D DRAM | HBM(3DスタックドDRAM) | 従来DRAM(DDR/GDDR) |

| 構造 | 前工程でセル積層 | TSVで垂直積層 | 2D平面 |

| 積層方式 | 前工程でセル積層 | TSV+マイクロバンプ | なし |

| 帯域幅 | HBM超の潜在帯域 | 800 GB/s〜2 TB/s | 50〜100 GB/s |

| レイテンシ | 最も低い | 低 | 中 |

| 容量拡張性 | 非常に高い | 中 | 高い |

| 消費電力 | 最も低い | 低 | 中〜高 |

| 製造難易度 | 極めて高い | 高 | 低 |

| 歩留まり | 低い | 中 | 高い |

| 主用途 | 将来のAI/HPC | GPU/AI/HPC | PC/サーバー |

| 量産状況 | 未量産 | 量産中 | 量産中 |

| 量産時期予測 | 2029〜2031 | — | — |

モノリシック3D DRAMをめぐる主要プレイヤー

モノリシック3D DRAMは、HBMの次を担う可能性がある技術として注目されていますが、2026年時点で本格的に研究開発を進めている企業は限られています。

特に、前工程の革新が必要となるため、ロジック・DRAM・NANDのすべてに強みを持つ企業や、3D構造の経験が豊富な企業が優位に立っています。

主なモノリシック3D DRAMメーカー(2026年時点)

2026年時点で、モノリシック3D DRAMに取り組む企業は以下の3社が中心です。

- Samsung Electronics(韓国)

- SK hynix(韓国)

- Kioxia(日本)

Micron Technologyは、HBMには積極的ですが、モノリシック3D DRAMに関する研究発表は限定的です。

主要メーカー比較

| 項目 | Samsung | SK hynix | Kioxia |

| 技術開発状況 | 最も積極的 2025年から開発加速 | 2030年頃の製品化を見据え研究加速 | 学会で新技術発表 研究段階(注目度が高い) |

| 目標量産時期 | 2020年代後半(最速) | 2030年頃 | 2030年代 |

| 強み | DRAM最大手の製造力 先端プロセスの実装力 HBM4の量産能力 | NVIDIAと強固な関係 HBM市場トップシェア 高歩留まり技術 | 3D NANDの発明者 セル積層技術の蓄積 材料・構造研究が強い |

| 弱み | HBMでSK hynixに遅れ 品質課題の歴史 | DRAM製造量はSamsungに劣る モノリシック3Dは研究段階 | DRAM事業の実績なし 量産経験ゼロ |

| HBMとの関係 | HBM4量産を強化中 | HBM市場シェア50%以上で圧倒的 | HBMは未参入 |

| 総合評価 | 最も早く量産に到達する可能性 | 後追いながらも有力な候補 | 長期的なダークホース |

「誰が勝つのか?」(2026年時点の予測)

結論として、モノリシック3D DRAMの勝者は 時期によって変わる と考えられます。

● 短期(〜2030):Samsungが最有力

- 最も早い量産ロードマップ

- 前工程の技術力が圧倒的

- HBM4量産で3D構造の知見が豊富

● 中期(2030〜2035):SK hynixが台頭

- HBM市場で圧倒的トップ(シェア50%以上)

- NVIDIAとの強固な関係

- 歩留まり技術が強い

● 長期(2035〜):Kioxiaがダークホース

- 3D NANDの発明者としてセル積層技術に強み

- DRAM未参入ゆえの“しがらみのなさ”

- 2030年代にDRAM参入の可能性

モノリシック3D DRAMとHBMに関わる装置メーカー・材料メーカー

モノリシック3D DRAMは、前工程の革新が不可欠な技術であるため、装置メーカー・材料メーカーの役割が従来以上に重要になります。

特に、高アスペクト比エッチング、コンフォーマル成膜、低温プロセス、ハイブリッドボンディング といった領域が鍵となり、HBMとは異なるプレイヤーが存在感を増しています。

主な装置・材料メーカー一覧表

| カテゴリ | 主要メーカー | 役割 | 対象技術 |

| 高アスペクト比エッチング | Lam Research TEL | DRAMキャパシタの深堀りエッチング | モノリシック3D DRAM |

| コンフォーマルALD | ASM Beneq TEL | 高誘電率膜の均一成膜 | モノリシック3D DRAM |

| 低温プロセス(BEOL CMOS) | Applied Materials TEL | 400℃以下でのCMOS形成 | モノリシック3D DRAM |

| ハイブリッドボンディング | EVG TEL | 層間接続の高密度化 | モノリシック3D DRAM・HBM |

| TSV形成 | Lam Research TEL | TSVエッチング・成膜 | HBM |

| マイクロバンプ | Shinko ASE Amkor | ダイ間接続 | HBM |

| インターポーザー | TSMC Samsung | CoWoS/SoICなどの先端パッケージ | HBM |

| テスト装置 | Advantest Teradyne | DRAM/HBMのテスト | HBM・DRAM共通 |

| 材料(高誘電率膜) | Merck Entegris | 高k材料の供給 | モノリシック3D DRAM |

| 材料(絶縁膜・金属膜) | JSR TOK DuPont | 配線・絶縁材料 | HBM・DRAM共通 |

モノリシック3D DRAMは「前工程メーカー」が主役になる

HBMは後工程(パッケージ)が中心ですが、モノリシック3D DRAMの成果を左右するポイントは前工程 です。

そのため、

- Lam Research(エッチング)

- TEL(エッチング・ALD・ボンディング)

- Applied Materials(成膜・CMP)

- ASM(ALD)

といった 前工程装置メーカーが最重要プレイヤー になります。

一方、HBMでは

- TSMC(CoWoS)

- ASE/Amkor(パッケージ)

- Shinko(基板)

など、後工程メーカーが中心です。

まとめ

モノリシック3D DRAMは、メモリ技術の限界を再定義する可能性を秘めていますが、低温CMOSやセル干渉など、克服すべき課題も多く残されています。

本コラムが示したように、技術的ハードルの理解は、将来の市場動向を読むうえで欠かせません。

読者の皆さまには、単なる“次世代技術”としてではなく、産業構造や投資判断に直結するテーマとして捉え、継続的に注目していただければ幸いです。