はじめに ― 半導体産業の大転換期

半導体産業は、これまで50年以上にわたって「ムーアの法則」と呼ばれるシンプルで力強い指針に従い、目覚ましい発展を遂げてきました。これは「およそ2年ごとに、チップに搭載されるトランジスタの数が2倍になる」という経験則で、性能の向上と製造コストの削減が同時に進む理想的なサイクルが長年維持されてきたのです。

しかし、10nm世代以降になると、この進化のスピードは急激に鈍り始めました。トランジスタをさらに小さくするための製造コストは非常に高くなり、使われる装置や材料にも限界が見え始めています。たとえば、EUV(極端紫外線)露光のような高度なリソグラフィ技術や、熱・電気の特性を細かく制御する技術など、従来の延長線上では対応しきれない課題が次々と浮かび上がってきています。

現在の技術開発の流れでは、7nmから5nm、そして2nmへと進むにつれて、単に回路の幅を狭くするだけでは乗り越えられない構造的・材料的な壁が立ちはだかっています。こうした状況に対して、各半導体メーカーは「微細化を進めるだけ」という従来のアプローチに頼るのではなく、複数の新しい技術を同時に進めることで、次のステージを目指しています。

具体的には、以下のような取り組みが進められています:

- GAAFETやCFETといった新しいトランジスタ構造によって、電気的な性能をより効率的に引き出す

- 異なる材料や機能を組み合わせることで、チップ全体の性能を高める

- チップレット技術や3Dパッケージングを活用して、限られたスペースを最大限に活かす

- AIや機械学習を使って設計を支援し、開発のスピードと精度を向上させる

このコラムでは、次世代の半導体製造に欠かせない主要技術について、以下のような観点からわかりやすく整理していきます:

- 技術の歴史と進化の流れ

- 各技術の基本的な仕組みと活用例

- 装置や材料を提供する企業の最新動向

- 現在直面している課題と、今後の展望

読者の皆さんには、単なる専門用語の理解にとどまらず、半導体業界全体の流れや構造的な変化を広い視点で捉えていただき、今後の技術選定や戦略づくりに役立てていただければ幸いです。

リソグラフィ技術 ― EUVからHigh-NAへ

光リソグラフィの発展と限界

リソグラフィは、半導体製造工程の中でも「心臓部」と称される極めて重要なプロセスです。

シリコンウェーハ上に微細な回路パターンを形成するために、光を用いて感光性樹脂(フォトレジスト)に回路図形を高精度に転写します。

この技術は世代ごとに使用する光源の波長を短縮することで、微細化を推進してきました:

- 1970年代:水銀ランプを用いた「g線(436nm)」および「i線(365nm)」が主流

- 1990年代:エキシマレーザーによる「KrF(248nm)」が導入され、解像度が飛躍的に向上

- 2000年代以降:「ArF(193nm)」が主流となり、さらに「ArF液浸リソグラフィ」ではレンズとウェーハの間に純水を満たすことで屈折率を高め、実効的な波長短縮を実現

しかし、193nmのArFでも理論的な解像度限界が近づき、7nm以降の世代では、ついにEUV(Extreme Ultraviolet:13.5nm)が導入され、次なる微細化ステージへの扉が開かれました。

EUVリソグラフィの特徴と課題

EUVは従来技術に比べて数倍の解像度を持ち、微細化の限界を突破する鍵となりましたが、その実用化には多くの技術的課題が存在しました:

- 光源の生成:EUV光は炭酸ガスレーザーでスズ(Sn)微粒子を蒸発・プラズマ化して発生させる特殊な方式を採用。高出力・安定性の確保が極めて困難で、光源開発には10年以上の歳月が費やされました。

- マスクの課題:EUV用マスクは反射型構造であり、透過型マスクと異なり欠陥検査・修復が難しく、歩留まりへの影響が大きい

- レジスト性能:感度・解像度・ラインエッジラフネス(LER)のバランスを取る必要があり、化学メーカーによる材料開発競争が加速

それでも、オランダのASML社が開発した「NXE」シリーズを中心に、TSMC・Samsung・Intelなどの主要ファウンドリがEUV装置を導入。現在の5nmおよび3nm世代の量産を支える中核技術となっています。

High-NA EUVの登場と展望

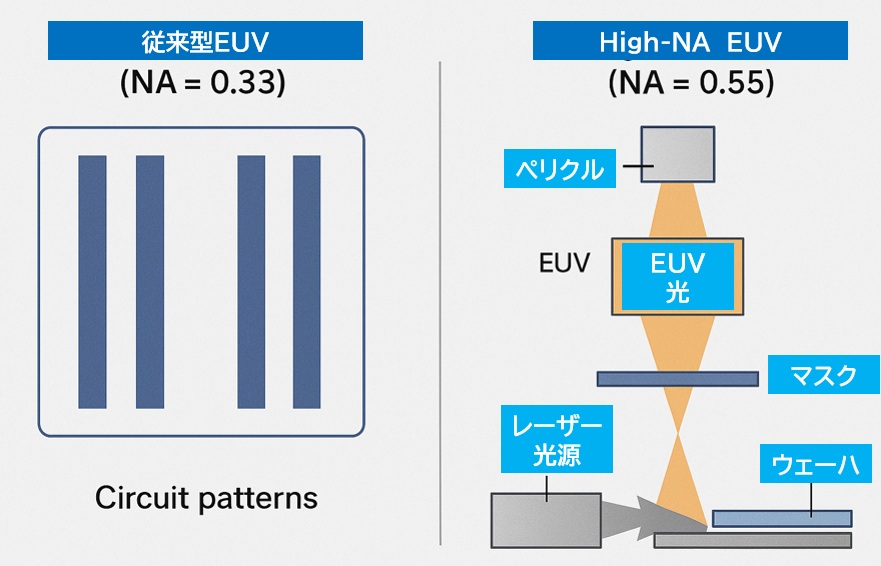

EUV技術の次なる進化形として注目されているのが、High-NA EUV(開口数0.55)です。これはレンズの開口数(Numerical Aperture)を従来の0.33から0.55へと拡張することで、さらなる解像度向上を目指すものです。

- Intelは2027年に世界初の量産導入を予定しており、次世代2nm以下の製造に向けた布石とされています。

- ただし、開口数の増加に伴い露光範囲が狭くなるため、チップを分割して露光し、後で接合する「ステッチング」技術が必要となるなど、新たな課題も浮上しています。

(ステッチング技術:露光範囲を超える大きなパターンを複数回に分けて露光し、精密につなぎ合わせる技術です。特に、マスクサイズやレンズの制限を超える大面積パターン形成に使われます。) - 装置の巨大化・高価格化も避けられず、導入企業の資本力と技術力が問われる局面となっています。

表:EUVリソグラフィの進化比較

| 項目 | 従来EUV (NA=0.33) | High-NA EUV (NA=0.55) |

| 解像度 | 約13nm | 約8nm |

| 装置価格 | 約200億円 | 約400億円以上 |

| 主導企業 | TSMC, Samsung, Intel | Intel(先行)、 TSMC(導入予定) |

| 主な技術課題 | 光源出力、マスク欠陥 | ステッチング、装置巨大化 |

成膜技術 ― ALDと新材料の台頭

ALDの重要性と進化

半導体の微細化が進むにつれ、膜厚の均一性や原子レベルでの制御精度が極めて重要な要件となっています。

特に、トランジスタ構造が3次元化し、極細配線や高アスペクト比構造が主流となる中で、従来のCVD(化学気相成長)やPVD(物理気相成長)では対応が困難な領域が増えています。

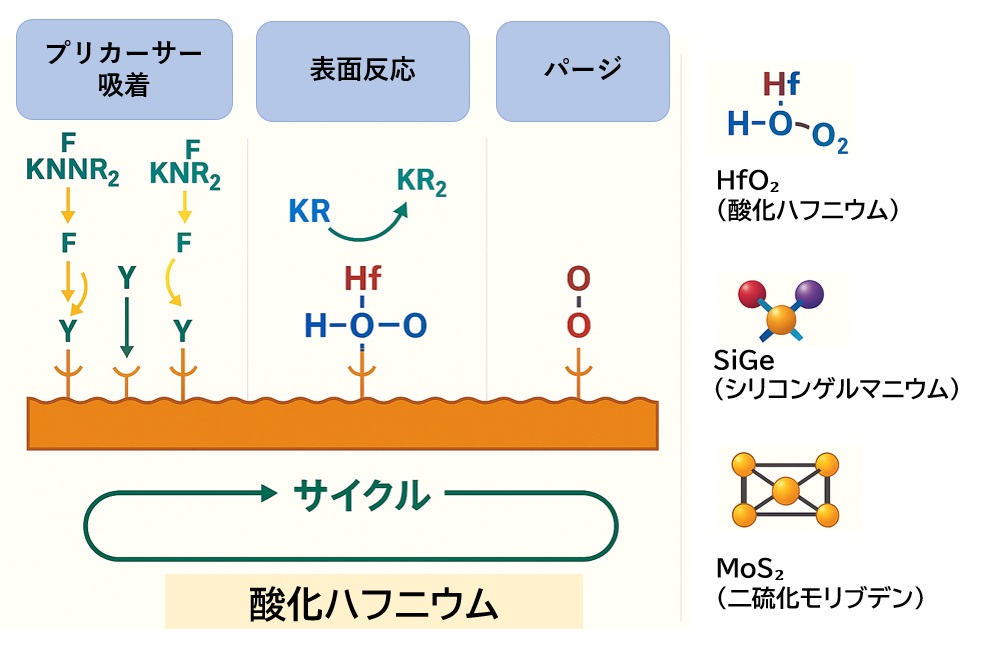

この課題を解決しているのが、ALD(原子層堆積:Atomic Layer Deposition)です。

ALDは、基板表面への吸着反応と除去反応を交互に繰り返すことで、1原子層ずつ薄膜を積層する手法です。このプロセスにより、以下のような利点が得られます。

- 極端に細い配線や3D構造の内壁でも、均一かつピンホールのない被覆が可能

- 膜厚の原子レベル制御が可能で、デバイス性能のばらつきを低減

- 高誘電率材料やバリア膜など、高機能材料の精密成膜に適している

ALDは、FinFETやGAAFETなどの先端トランジスタ構造において、ゲート絶縁膜・スペーサー・キャップ層など多岐にわたる用途で活用されています。

新材料の導入動向と成膜技術の役割

シリコンベースの材料では物理的・電気的限界が見え始めており、次世代半導体では多様な新材料の導入が加速しています。

ALDはこれら新材料の成膜にも対応可能であり、以下のような材料が注目されています:

- 高誘電率材料(High-k):HfO₂(ハフニウム酸化物)などは、ゲート酸化膜として不可欠。絶縁性と誘電率の両立が求められる

- SiGe(シリコンゲルマニウム):キャリア移動度の向上を目的に、Intelが次世代ノードで積極採用

- III-V族化合物(InGaAsなど):高移動度チャネル材料として、高速・低消費電力化に貢献

- 2D材料(MoS₂、WS₂など):原子層レベルの厚みを持つ「ポストシリコン」候補。Samsungや各国の研究機関が開発を進行中

成膜技術は、微細化と材料革新の交点に位置する重要技術であり、装置メーカー各社(LAM Research、Applied Materials、東京エレクトロン)は、ALD装置の精度・スループット・材料対応力を競い合っています。

エッチング技術 ― 原子層エッチング(ALE)

ALEの基本原理と優位性

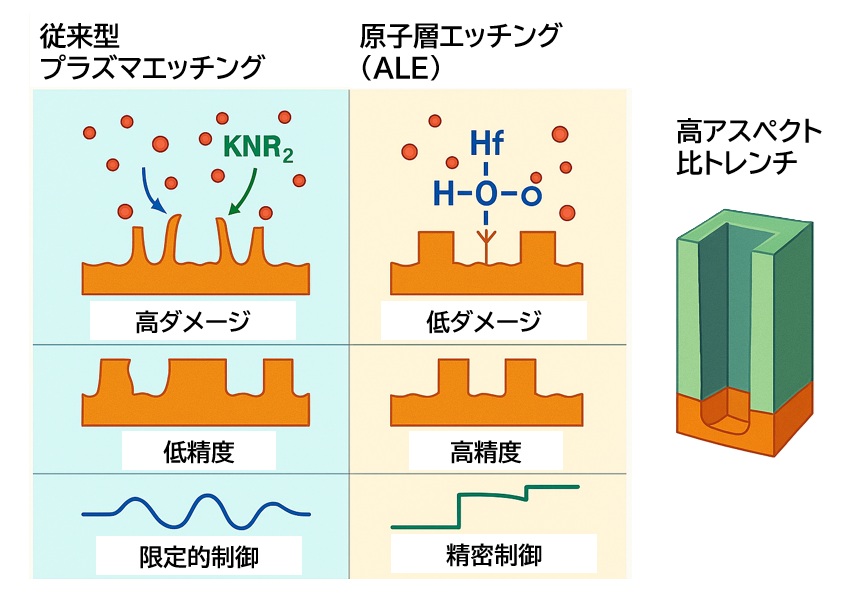

ALE(原子層エッチング:Atomic Layer Etching)は、ALDと対をなす技術であり、原子層単位で材料を選択的に除去するプロセスです。

吸着と反応除去を交互に行うことで、極めて高い制御性と選択性を実現します。

従来のプラズマエッチングでは、微細加工時に以下のような課題がありました:

- 過剰なエッチング(オーバーエッチ)による寸法誤差

- プラズマダメージによる材料特性の劣化

- 高アスペクト比構造での均一性確保が困難

ALEはこれらの課題を克服し、2nm世代以降の製造において不可欠な技術と位置づけられています。

ALEの産業応用と装置動向

ALEはすでに量産ラインでの導入が進んでおり、以下のような応用例が報告されています:

- TSMC:EUVリソグラフィ後のパターン形成工程にALEを導入し、寸法精度とエッチング均一性を確保

- Samsung:GAAFET構造のチャネル形成にALEを活用し、デバイス性能の安定化を図る

- 装置メーカー:LAM ResearchがALE技術のリーディングカンパニーとして先行。東京エレクトロン(TEL)は高アスペクト比対応ALE装置で市場拡大中

このように、ALEは微細加工の精度を飛躍的に高める技術として、次世代ノードの製造において「必須技術」としての地位を確立しつつあります。

トランジスタ構造 ― FinFETからGAAFETへ

FinFETの限界と役割

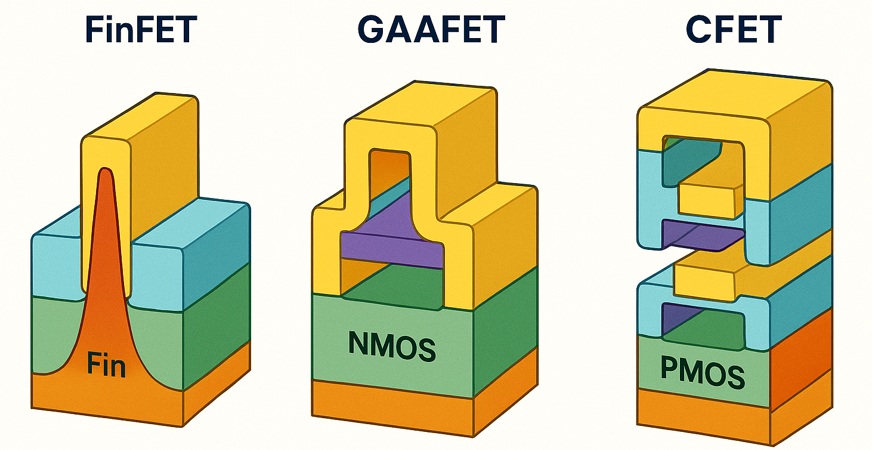

FinFET(フィン型電界効果トランジスタ)は、22nm世代から本格導入された3次元構造のトランジスタです。シリコン基板上にフィン状のチャネルを立ち上げ、ゲート電極が三方向からチャネルを囲むことで、以下のような利点を実現しました。

- リーク電流の大幅な抑制:ゲート制御性が向上し、待機電力の低減に貢献

- 省電力化と高性能化の両立:スマートフォンやサーバー向けSoCに広く採用

- 製造プロセスの成熟:10nm~7nm世代まで主流技術として活躍

しかし、チャネル幅が数nmレベルに迫ると、以下のような課題が顕在化します。

- ゲート制御性の限界(チャネル全体を囲めない)

- キャリア移動度の低下

- 微細化による構造的制約と製造難易度の上昇

GAAFET ― 次世代トランジスタの本命

GAAFET(Gate-All-Around FET)は、FinFETの構造的限界を克服する次世代トランジスタです。チャネルをナノシート構造またはナノワイヤ構造で形成し、ゲートが全周囲からチャネルを包み込むことで、電流制御性を最大化します。

| 特徴 | 内容 |

| 全周囲ゲート | チャネル全体を360度囲むことで、電流制御性が飛躍的に向上 |

| 微細化対応 | 3nm以下のノードでも安定した動作が可能 |

| 高性能・低消費電力 | FinFET比でさらなる性能向上と省電力化が期待される |

Samsungは2022年に3nm世代で世界初のGAAFET量産を実現。TSMCも2nm世代での採用を予定、ラピダスもIBMと共同で2027年量産開始を計画しており、業界全体がGAAFETへの移行を進めています。

CFET ― 積層型トランジスタの未来

GAAFETの次に登場する可能性があるのが、CFET(Complementary FET)です。これは、NMOSとPMOSを垂直方向に積層することで、面積効率を飛躍的に高める革新的アーキテクチャです。

| 項目 | 内容 |

| 積層構造 | NMOSとPMOSを上下に配置し、チップ面積を削減 |

| 性能向上 | 配線長の短縮により、遅延・消費電力を低減 |

| 研究機関 | IMECやIBMが試作を進行中。2030年以降の実用化が期待される |

CFETは、3D集積技術や先端パッケージングとの融合が前提となるため、製造技術・設計手法の革新が求められます。

パッケージングと異種集積

パッケージングの重要性

従来、性能向上は微細化に依存していました。

しかし現在は、異種チップを効率的につなぐパッケージング技術が性能を左右する重要な技術となっています。

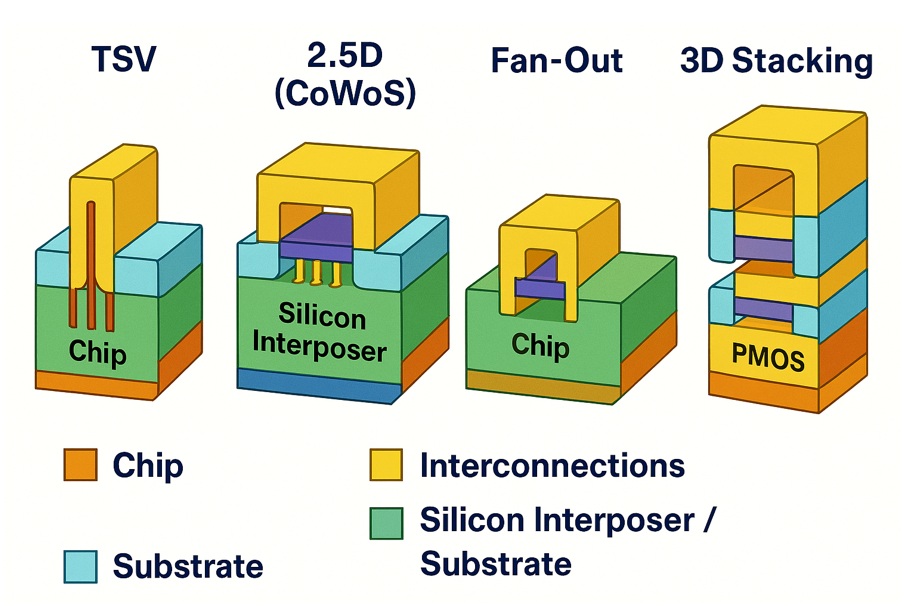

表:技術比較表

| 技術 | 特徴 | 採用企業 |

| TSV (Through-Silicon Via) | ウェーハ貫通配線、メモリとロジックの直結 | HBMメモリ、TSMC、Samsung |

| 2.5D(CoWoS等) | シリコンインターポーザ上に複数チップ搭載 | TSMC(CoWoS)、Intel(EMIB) |

| Fan-Out | インターポーザ不要で小型化 | TSMC InFO、ASE |

| 3D積層(Foveros、SoIC) | ロジック同士の垂直積層 | Intel(Foveros)、 TSMC(SoIC) |

計測とプロセス制御 ― 原子レベルの精度を支える技術

微細化とともに高まる計測の重要性

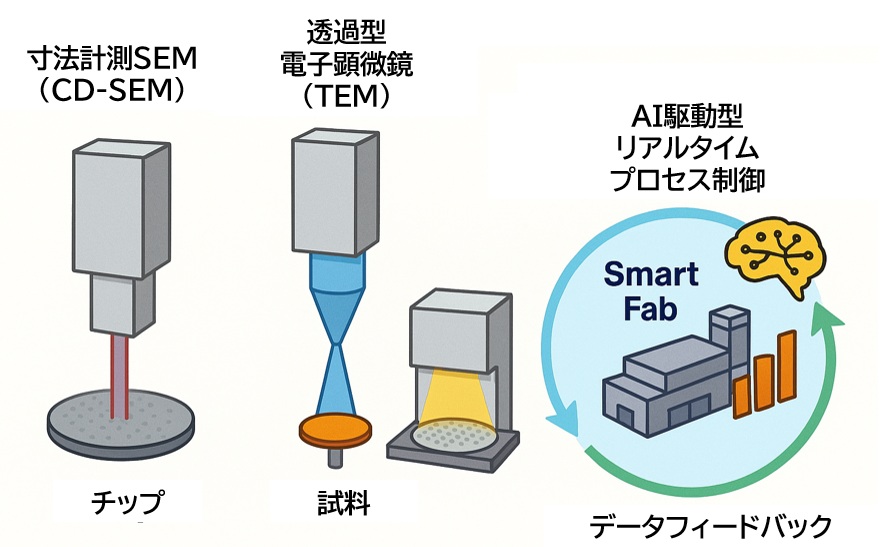

半導体製造が原子レベルの寸法制御を求める時代に突入する中で、計測技術とプロセス制御の役割はますます重要になっています。ナノスケールでの加工精度を確保するには、欠陥の検出、寸法の計測、材料の構造解析など、あらゆる工程で高精度なモニタリングが不可欠です。

主な計測技術とリーディング企業

| 分野 | 技術・装置 | 主な企業 | 役割 |

| 欠陥検査 | 光学式・電子線式検査装置 | KLA | ウェーハ表面やパターンの欠陥検出。世界市場のトップシェアを維持 |

| 寸法計測 | CD-SEM(Critical Dimension SEM) | 日立ハイテク | 微細パターンの寸法をnm単位で計測。業界標準機として広く採用 |

| 材料解析 | TEM(透過型電子顕微鏡) | Thermo Fisher Scientific | 原子配列や界面構造の解析に不可欠。材料開発や故障解析に活用 |

これらの装置は、製造工程の各ステップでプロセスウィンドウの最適化や歩留まり改善に直結するデータを提供します。

AIによるリアルタイム制御 ― 次世代ファブの姿

従来の計測は「事後検証」が中心でしたが、現在はAIを活用したリアルタイムフィードバック制御が急速に進化しています。これにより、製造中に得られるデータを即座に解析し、プロセス条件を動的に調整することが可能となっています。

| 企業 | コンセプト | 内容 |

| TSMC | データ駆動型ファブ | 製造装置・検査装置からのデータを統合し、AIで最適化。歩留まりとスループットを同時に向上 |

| Intel | デジタルツイン | 実際の製造ラインと仮想モデルを同期させ、シミュレーションと制御を融合。設計~製造の一体化を目指す |

これらの取り組みは、2nm世代以降の製造において、品質・コスト・スピードの三立を実現する鍵となります。

サプライチェーンと周辺産業 ― 半導体製造を支える縁の下の技術力

製造装置だけでは成り立たない半導体産業

半導体製造は、露光装置や成膜・エッチング装置などの前工程装置だけで完結するものではありません。実際には、素材・部品・搬送・検査・環境制御など、数多くの周辺産業が連携することで、ナノスケールの精密加工が可能となっています。

とりわけ、EUV(極端紫外線)リソグラフィの導入以降、サプライチェーンの高度化と専門化が急速に進んでいます。

注目すべき周辺技術と日本企業の貢献

| 分野 | 製品・技術 | 主な企業 | 役割 |

| EUVペリクル | EUV光を透過する保護膜 | HOYA(日本) | 世界市場をほぼ独占。露光工程でのマスク保護に不可欠 |

| EUVレジスト | 感光性材料 | JSR、 東京応化工業(日本) | EUV対応の高感度・高解像度レジストを供給。ASMLとの共同開発も進行 |

| 高純度ガス | 成膜・エッチング用プロセスガス | 昭和電工マテリアルズ、Air Liquide | 数ppbレベルの不純物管理が求められる。製造歩留まりに直結 |

| 搬送システム | ウェーハ搬送・保管装置 | 村田機械、三菱電機 | クリーン環境下での自動搬送を実現。ファブの効率化に貢献 |

これらの分野では、日本企業が素材・部品の供給において不可欠な存在となっており、グローバルな半導体サプライチェーンの中核を担っています。

サプライチェーンの進化と戦略的価値

微細化・多層化・3D構造化が進む中で、周辺産業の役割は単なる“補助”ではなく、製造技術の一部として統合的に設計されるべき領域となっています。特に以下の点が重要です:

- 装置との協調設計:ペリクルやレジストは露光装置との相互最適化が必要

- 品質トレーサビリティ:高純度ガスや搬送装置は、リアルタイム監視・履歴管理が求められる

- 地政学的リスク対応:素材・部品の供給安定性が、国家戦略レベルで注目されている

日本企業は、こうした高信頼・高精度な素材技術において世界的な競争力を持ち、今後も不可欠なパートナーとしての地位を維持・強化していくことが期待されます。

環境対応とサステナビリティ ― 半導体産業の責任と革新

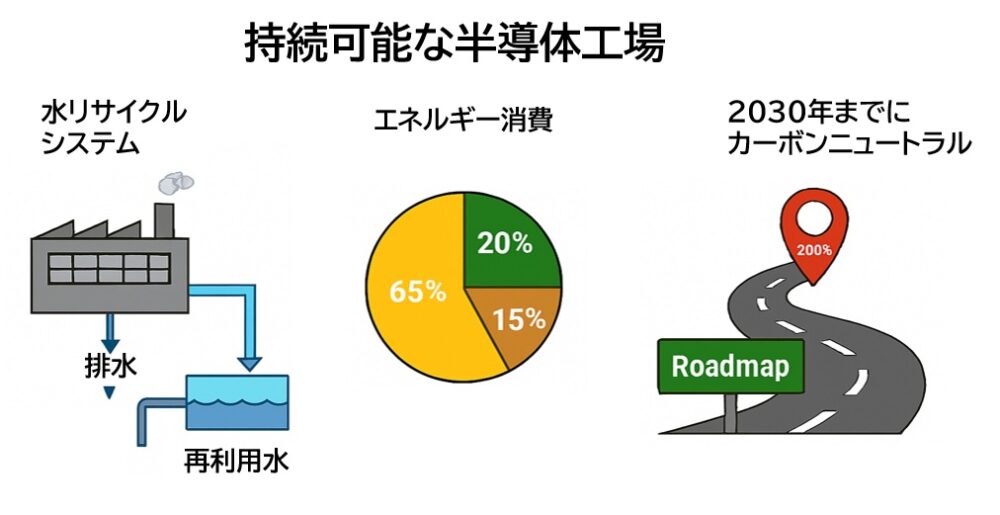

半導体ファブの環境負荷と課題

先端半導体の製造には、膨大な電力・超純水・化学薬品・ガスが必要とされます。特にEUVリソグラフィや原子層プロセスの導入により、クリーンルームのエネルギー消費や水使用量は急増しています。

| 資源 | 使用例 | 環境負荷 |

| 電力 | クリーンルーム維持、プラズマ装置 | CO₂排出量の増加 |

| 水 | 超純水洗浄、冷却 | 地域の水資源圧迫 |

| 化学薬品・ガス | 成膜・エッチング・洗浄 | 廃液・温室効果ガスの排出 |

このような背景から、環境対応はもはやCSR(企業の社会的責任)の枠を超え、顧客企業からの調達条件や政府・地域との協調要件として位置づけられつつあります。

主要企業の取り組み事例

| 企業 | 施策 | 内容 |

| TSMC | 水資源リサイクル | 台湾の水不足対策として、リサイクル率85%以上を達成。ファブ内での水循環システムを高度化 |

| Intel | カーボンニュートラル宣言 | 2030年までにScope 1・2の排出ゼロを目指す。再生可能エネルギー導入と製造プロセスの最適化を推進 |

| LAM Research | 温室効果ガス削減技術 | プラズマ装置からのPFC(パーフルオロ化合物)排出削減技術を開発。装置レベルでの環境負荷低減を提案 |

これらの取り組みは、製造コストや技術選定に直結する要素となっており、環境対応が競争力の一部として認識され始めています。

サステナビリティの新潮流 ― 技術と経営の融合

環境対応は単なる「善意」ではなく、以下のような戦略的価値を持ちます。

- サプライチェーン全体での環境評価:顧客企業はScope 3(間接排出)まで含めた評価を実施

- AIによるエネルギー最適化:製造装置の稼働状況をリアルタイムで分析し、消費電力を最小化

- グリーンファブ構想:再生可能エネルギー・水循環・廃棄物ゼロを目指す統合型製造施設の設計が進行中

今後は、環境対応=技術革新の一部として、装置設計・材料選定・プロセス開発のすべてに組み込まれていくことが予想されます。

地政学と政策動向 ― 半導体は国家戦略の中核へ

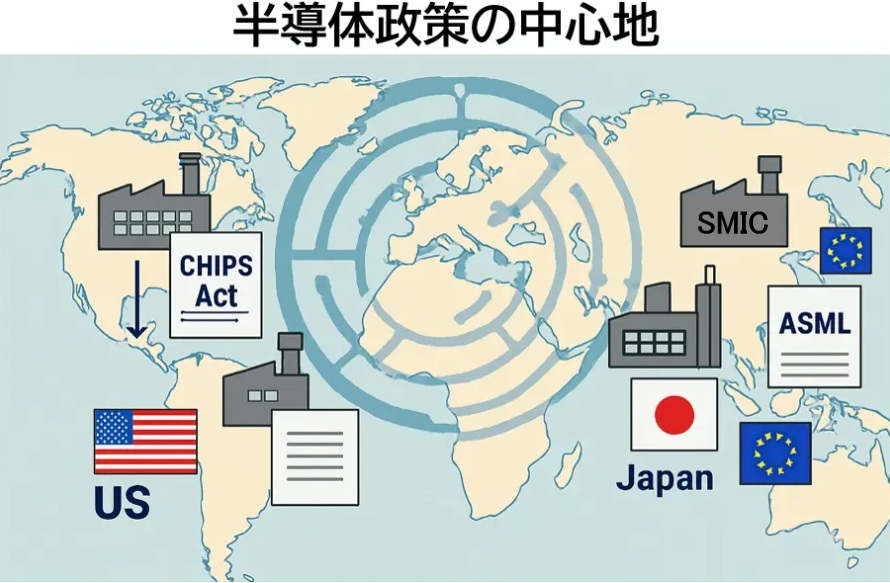

技術競争から国家戦略へ

半導体はもはや単なる産業技術ではなく、経済安全保障・外交・産業政策の要として、各国政府が直接関与する戦略分野となっています。製造拠点の分散、技術の囲い込み、輸出規制、補助金政策など、地政学的な動きが産業構造に大きな影響を与えています。

各国の政策動向と戦略的取り組み

| 地域 | 主な施策・動向 | 内容 |

| 米国 | CHIPS Act(2022年成立) | 半導体製造の国内回帰を推進。Intel・TSMCがアリゾナ州で工場建設中。最大520億ドル規模の補助金を投入 |

| 中国 | 技術自立と輸出規制の影響 | SMICが14nm世代まで到達。ただし、EUV露光装置の輸入規制により先端ノードの開発は停滞 |

| 日本 | Rapidusによる先端製造挑戦 | 2nm世代の量産を目指し、IBM・IMECと協業。経済産業省が数千億円規模の支援を実施 |

| 欧州 | ASMLを軸とした技術戦略 | EUは半導体法(European Chips Act)を策定。ASMLがEUV露光装置で世界的地位を確立し、独自戦略を模索中 |

これらの動きは、単なる産業政策にとどまらず、外交・安全保障・通商戦略と密接に連動しています。

半導体と経済安全保障 ― 技術の地政学化

半導体は、以下のような理由から経済安全保障の中核技術と位置づけられています。

- 軍事・通信・AIへの応用:先端半導体はレーダー、量子計算、暗号通信などに不可欠

- 技術の囲い込みと輸出管理:米中間の技術摩擦により、装置・材料・IPの流通が制限される

- 製造拠点の分散とリスク分散:地政学的リスクに備え、各国が国内製造能力の確保を急ぐ

今後は、技術力だけでなく政策対応力・外交戦略との整合性が、企業の競争力を左右する要素となっていくでしょう。

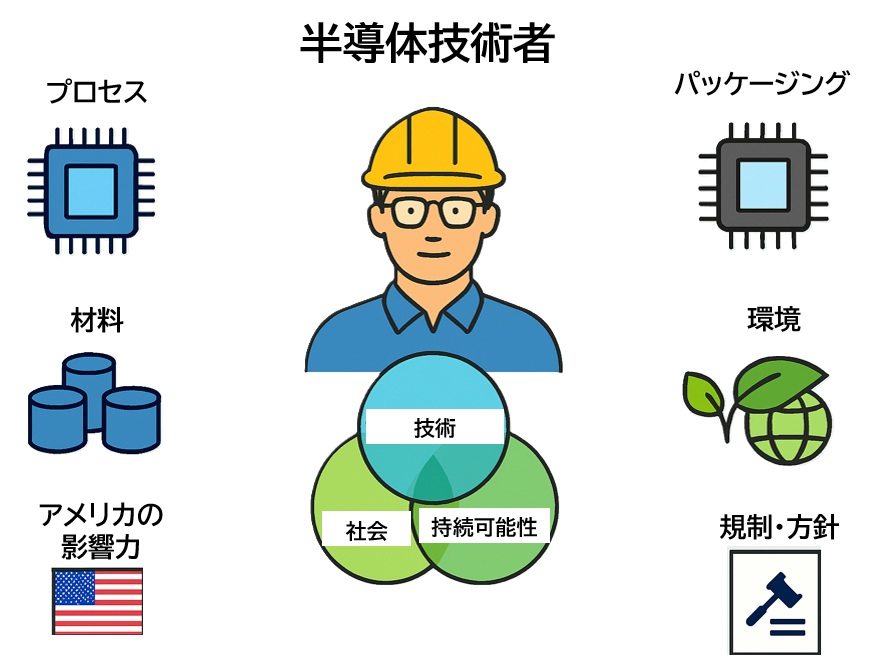

まとめ ― 技術者が持つべき視座と未来への構え

多次元化する半導体技術の本質

次世代半導体は、もはや単なる「微細化競争」の延長線上にはありません。製造プロセス、材料革新、パッケージング技術、環境対応、地政学的政策――これらが複雑に絡み合う多次元の技術領域へと進化しています。

このような状況下では、技術者に求められる資質も大きく変化しています。

技術者に求められる新たな視点・視野

| 視点・視野 | 内容 |

| 俯瞰力 | 自分の専門領域に閉じず、製造全体の流れや業界構造を理解する力 |

| 異分野連携力 | 材料・装置・設計・政策など、異なる技術領域との接点を持ち、協働できる柔軟性 |

| 技術と社会の接続力 | 技術が環境・経済・安全保障に与える影響を理解し、社会的価値を意識した判断ができること |

| 未来志向と学習力 | 技術トレンドの変化に対応し、継続的に学び直す姿勢と情報感度 |

技術者は単なる“工程担当者”ではなく、技術と社会をつなぐ橋渡し役としての役割を担う時代に入っています。

現場から始まるイノベーション

現場での観察力、実装力、改善力は、依然として技術者の核です。しかしそれに加えて、全体最適の視点と多様なステークホルダーとの対話力が、今後の技術者像を形づくっていくでしょう。