先進後工程で注目される「3大材料技術」とは?

半導体産業は長年にわたり、微細化による性能向上を追求してきました。

しかし、EUV(極端紫外線)露光技術を用いた7nmや5nmといった超微細領域では、製造コストの高騰や歩留まりの低下といった課題が顕在化しつつあります。

こうした限界を打破する手法として、近年注目されているのが「先進後工程(Advanced Packaging)」です。

これは、複数のチップを高密度かつ高精度に接続することで、システム全体の性能や機能を向上させる技術アプローチです。

この先進後工程を支える重要な材料技術として、「フォトレジスト」「CMPスラリー」「銅張積層板(CCL)」の三つが挙げられます。

これらはそれぞれ、以下の工程において不可欠な役割を担っています。

- フォトレジスト:微細な回路パターンを形成するための感光性材料。露光・現像工程において高精度な描画を実現。

- CMPスラリー:化学機械研磨(Chemical Mechanical Polishing)に用いられる研磨液。多層構造の平坦化により、接続精度と信頼性を確保。

- 銅張積層板(CCL):配線基板の構成材料。高周波対応や熱伝導性など、実装工程における性能向上に寄与。

これら三大材料は、先進後工程の各ステップにおいて不可欠な存在でです。

先進後工程とは?前工程との違いと重要性

従来の半導体製造は、シリコンウエハ上にトランジスタや配線を形成する「前工程」と、チップをパッケージ化する「後工程」に分かれていました。

しかし、現在は「WLP(Wafer Level Package)」や「PLP(Panel Level Package)」など、ウエハレベルでのパッケージ形成が一般化しつつあります。

さらに、「2.5D実装」「3D積層」「ハイブリッドボンディング」などの技術により、チップ同士を垂直方向に積み重ねることも可能になりました。

これにより、信号遅延を減らし、消費電力を抑えた高性能チップが実現します。

ただし、こうした先進後工程では、従来の材料では対応できない課題が多く発生します。

たとえば、

- 低温での高密着性

- 微細なライン形成に対応するレジスト

- 平坦性を極限まで追求するCMPスラリー

- 熱膨張の少ない高機能基板

といった要件です。

フォトレジスト ― 微細パターン形成の精度を左右する重要材料

フォトレジストとは、光照射によって化学反応を起こし、半導体ウエハ上に微細な回路パターンを形成する感光性材料です。

前工程では、EUV(極端紫外線)やArF(193nm)露光技術に対応した高解像度レジストが用いられますが、先進後工程では、異なる特性が求められます。

厚膜レジストの役割と種類

後工程では、再配線層(RDL: Redistribution Layer)やマイクロバンプ形成など、凹凸の大きい表面構造を扱うため、厚膜タイプのフォトレジストが使用されます。

これにより、段差への追従性や加工性が向上し、安定したパターン形成が可能になります。

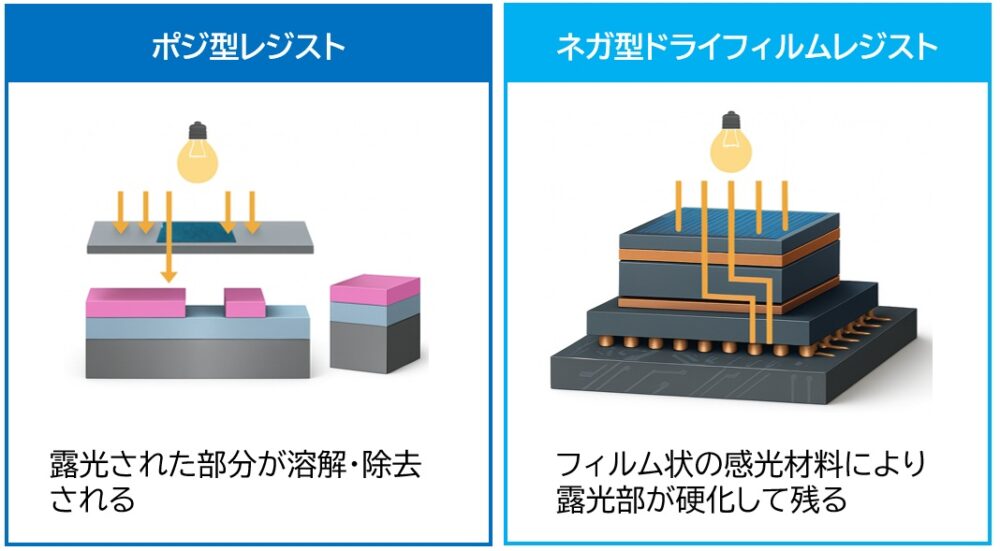

主なレジストタイプは以下の通りです:

- ポジ型レジスト:露光された部分が溶解・除去されるタイプ。高精度なパターン形成に適しており、微細配線やRDL形成に広く用いられます。

- ネガ型ドライフィルムレジスト:フィルム状の感光材料で、露光部が硬化して残るタイプ。厚膜対応に優れ、段差追従性やラミネート性が高く、マイクロバンプ形成などに適しています。

主要メーカーと技術動向

フォトレジスト分野では、日本企業が高い競争力を持っています:

- 東京応化工業(TOK)

- JSR

- 信越化学工業

海外では以下の企業が代表的です:

- DuPont

- Rohm and Haas(現DuPont傘下)

近年の技術開発では、以下の性能が重視されています:

- 低残渣性:ハイブリッドボンディングなどの接合工程で、残渣が接合不良の原因となるため、洗浄性の高さが重要。

- 高アスペクト比対応:微細かつ高密度な構造形成に対応するための厚膜加工性。

- 熱安定性:後工程での加熱処理に耐える材料設計。

これらの特性を備えたフォトレジストは、先進後工程の信頼性と量産性を支える重要性を増していくと考えられます。

CMPスラリー ― 平坦化を極めるナノ研磨技術

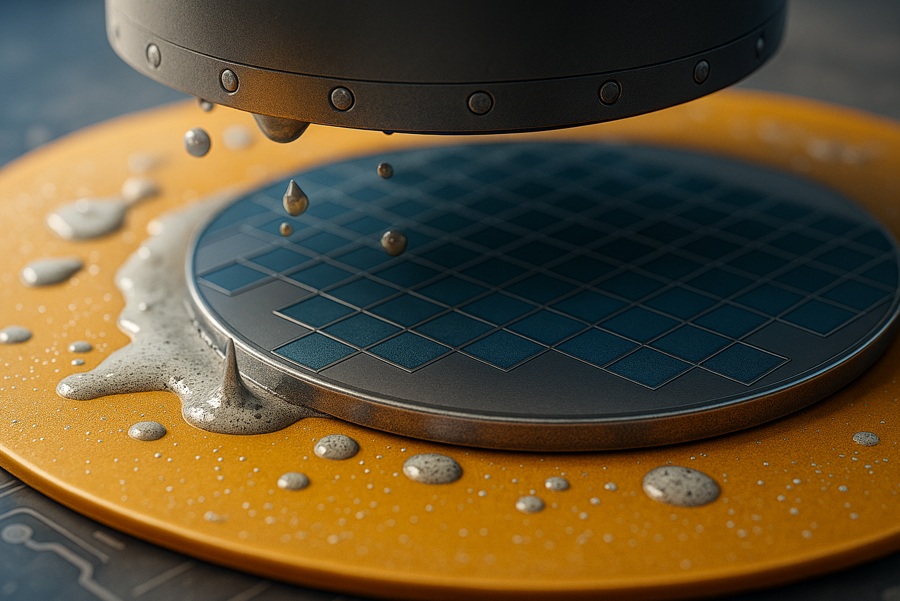

CMP(Chemical Mechanical Polishing)は、半導体ウエハの表面をナノレベルで平坦化するための重要なプロセスです。

配線層や絶縁層の形成後に実施され、表面の凹凸を均一に整えることで、次工程の露光・接合精度を確保し、デバイスの信頼性と性能を向上させます。

スラリーの構成と機能

CMPスラリーは、研磨材と化学薬品を混合した懸濁液で構成され、物理的な研磨と化学的な反応を組み合わせて平坦化を実現します。

主な構成要素は以下の通りです。

- 研磨材:シリカ(SiO₂)やアルミナ(Al₂O₃)などの微粒子。表面を機械的に削る役割を担います。

- 酸化剤:金属表面を化学的に軟化させ、研磨材との反応性を高めます。

- 腐食抑制剤・分散剤:表面の過剰な腐食や粒子の凝集を防ぎ、均一な研磨を促進します。

スラリーの粒径分布やpH値を精密に制御することで、研磨速度と表面粗さのバランスを最適化し、欠陥の少ない仕上がりを実現します。

用途別CMPスラリーの分類

CMPは対象材料や工程に応じて複数の種類が存在します。

代表的な用途は以下の通りです。

- Cu-CMP:銅配線層の研磨

- W-CMP:タングステンバリア層の研磨

- SiO₂-CMP:絶縁膜(酸化膜)の研磨

これらはそれぞれ異なる化学反応性や研磨条件が求められるため、専用スラリーの設計が不可欠です。

主要用途とメーカー

CMPスラリー市場では、以下の企業が世界的に高いシェアを誇ります。

- Entegris(旧Cabot Microelectronics)

- Fujimi(日本)

- DuPont

- Versum Materials(現Merck傘下)

近年の技術開発では、以下のテーマが重視されています:

- 低欠陥化:パーティクルやスクラッチの発生を抑制し、歩留まりを向上

- 環境対応型スラリー:廃液処理や安全性に配慮した成分設計

- ファンアウト実装対応:基板反りを抑えるため、研磨圧と化学反応性のバランス設計が重要

CMPスラリーは、先進後工程の精度・信頼性・量産性を支える基盤技術として、今後ますます重要性を増していく分野です。

銅張積層板(CCL) ― パッケージ基板の性能を左右する基盤材料

銅張積層板(CCL:Copper Clad Laminate)は、樹脂と銅箔を積層した材料で、パッケージ基板やプリント配線板のベースとなります。

先進後工程では、チップと基板をつなぐインターポーザやFC-BGA(Flip Chip Ball Grid Array)などに使用されます。

銅張積層板は、絶縁樹脂層と銅箔を積層した複合材料であり、プリント配線板やパッケージ基板のベース素材として広く使用されています。

先進後工程においては、インターポーザやFC-BGAなど、チップと基板を高密度に接続する構造に用いられ、信号伝送や放熱の観点から重要な役割を担います。

CCLの構成と特性

基本構造は「絶縁樹脂層+銅箔」からなり、樹脂層の特性が信号品質や熱特性を大きく左右します。

高性能パッケージでは、次の特性が重要です。

- 低誘電率(Dk)・低誘電損失(Df):高周波信号の伝送損失を低減

- 低熱膨張(CTE):チップとの接合安定性を確保

- 高放熱性:AIサーバーなど高発熱用途への対応

CCLの基本構造は「絶縁樹脂層+銅箔」で構成されており、特に樹脂層の物性が信号品質や熱管理性能に大きく影響します。

高性能パッケージ基板に求められる主な特性は以下の通りです:

- 低誘電率(Dk)・低誘電損失(Df):高周波信号の伝送損失を抑え、通信速度と信号整合性を向上

- 低熱膨張係数(CTE):温度変化による寸法変化を抑制し、チップとの接合信頼性を確保

- 高放熱性:AIサーバーや高性能演算処理向けの発熱対策に対応

これらの特性は、パッケージの信頼性・性能・実装密度を左右する重要な要素です。

絶縁材の種類と主要メーカー

CCLに使用される絶縁樹脂には、以下のような種類があります。

- エポキシ樹脂:汎用性が高く、コストパフォーマンスに優れる

- BTレジン(ビスマレイミドトリアジン):低CTE・高耐熱性に優れ、高密度実装に適応

- ポリイミド:高耐熱性・柔軟性を持ち、特殊用途に対応

主なCCLメーカーと代表製品は以下の通りです。

| メーカー名 | 主な製品・特徴 |

| Panasonic | MEGTRONシリーズ:低Dk・低Df・高信頼性 |

| 三菱ガス化学 | GMCシリーズ:高耐熱・高放熱性 |

| 南亜電子(Nan Ya) | 汎用CCLから高機能品まで幅広く展開 |

| Doosan | 高密度配線対応の低誘電材料 |

| Isola | 高周波・高速伝送向けの先端材料 |

技術動向と今後の展開

近年では、さらなる高密度配線や微細化に対応するため、以下のような新材料の開発が進んでいます。

- ガラス基板:寸法安定性と表面平滑性に優れ、次世代パッケージ基板として注目

- ハイブリッド積層材料:異種樹脂の複合化により、電気・熱・機械特性を最適化

これらの材料技術は、先進後工程の進化に伴い、パッケージ基板の性能向上と信頼性確保に不可欠な要素となっています。

3つの材料の“相互作用”が生む技術統合の難しさ

フォトレジスト、CMPスラリー、銅張積層板はそれぞれ独立した技術のように見えますが、実際には互いに強く影響し合います。

たとえば、CMP後の表面粗さがフォトレジストの密着性に影響したり、基板材料の熱膨張係数がフォトリソ精度を狂わせたりします。

このため、先進後工程では「材料間の整合性設計(Co-Design)」が求められています。

さらに、AIシミュレーションによるプロセス最適化や、マルチスケールモデリングを活用した材料設計も進展中です。

これにより、試作コストを抑えつつ、より信頼性の高いパッケージ設計が可能になりつつあります。

フォトレジスト、CMPスラリー、銅張積層板(CCL)は、それぞれ異なる工程で使用される独立した材料技術に見えます。

しかし、先進後工程においては、これらの材料が互いに密接に影響し合うため、単独での最適化では不十分です。

たとえば、

- CMP後の表面粗さがフォトレジストの密着性やパターン形成精度に影響を及ぼす

- 基板材料の熱膨張係数(CTE)がフォトリソグラフィ工程における寸法精度や位置合わせに干渉する

- レジスト残渣が後工程の接合信頼性に影響するなど、工程間の連携が不可欠です

材料整合性設計(Co-Design)の重要性

こうした複雑な相互作用を踏まえ、材料間の整合性設計(Co-Design)が求められています。

これは、個別材料の性能だけでなく、工程全体での相互適合性を考慮した設計手法であり、以下のような技術が活用されています。

- AIシミュレーション:材料特性とプロセス条件の組み合わせを仮想的に検証し、最適解を探索

- マルチスケールモデリング:ナノスケールからパッケージ全体までの挙動を統合的に解析し、設計精度を向上

- デジタルツイン技術:実装環境を仮想空間で再現し、試作レスでの検証を可能に

これにより、試作コストの削減と設計信頼性の向上が両立でき、先進後工程の量産化に向けた技術基盤が整いつつあります。

未来 ― 材料開発が左右する先進パッケージの競争力

今後の半導体産業における競争力は、「設計」や「製造装置」だけでなく、材料技術の優位性によっても大きく左右されるようになります。

特に、先進パッケージ技術の進展に伴い、以下の材料開発が重要なテーマとして注目されています。

- ハイブリッドボンディング対応材料:極限までの表面平滑性と清浄度が求められ、接合信頼性の確保に直結

- 低温接合用レジスト・接着層:熱履歴を最小限に抑えつつ、機械的・電気的な接合強度を維持

- リサイクル対応スラリーや環境低負荷型樹脂:持続可能性と環境規制への対応を両立する次世代材料

日本企業の材料技術が持つ競争優位性

化学材料分野において、日本企業は長年にわたり高い技術力と品質管理能力を培ってきました。

半導体製造装置や設計分野では海外企業の存在感が強まる一方で、材料技術は日本企業が再び主導権を握る可能性が高い領域といえます。

特に以下の点で競争力が期待されています。

- 高純度・高均質な材料製造技術

- 微細加工に対応した精密材料設計

- 顧客ニーズに応じたカスタマイズ対応力

- 環境対応・安全性への先進的な取り組み

これらの強みを活かすことで、日本企業は先進パッケージ分野においてグローバル競争の中核的存在となる可能性を秘めています。

まとめ ― 材料技術は先進後工程を支える“見えない主役”

フォトレジスト、CMPスラリー、銅張積層板(CCL)は、いずれも半導体パッケージの根幹を支える重要材料です。

工程ごとに役割は異なりますが、これらの材料がなければ、ナノレベルの微細配線、3D積層構造、高信頼性の接合技術は成立しません。

まさに、最終製品の性能を左右する“見えない主役”といえます。