近年、半導体業界では微細化の限界や高性能化の要求が急速に高まり、製造プロセスの重点が「前工程」から「後工程」へとシフトしつつあります。

特に、スマートフォンやAIチップ、車載向け半導体などでは、チップの機能や性能だけでなく、パッケージング技術そのものが製品競争力を左右する時代になっています。

その中でも、WLP(Wafer Level Packaging)やPLP(Panel Level Packaging)といった新しい後工程手法は、ニュースや展示会でも頻繁に取り上げられる話題です。

本記事では、これらの技術の基礎と違い、そして次世代パッケージングの展望について整理して解説します。

半導体パッケージ後工程とは

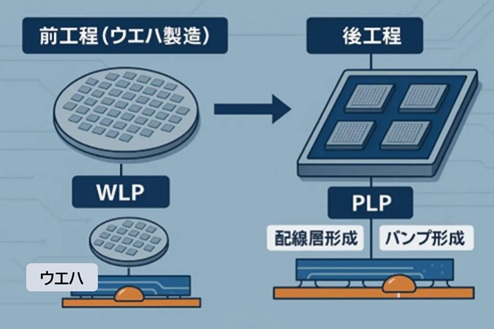

半導体チップは、ウエハ上で回路を形成する「前工程」を終えた後、切り出して使いやすい形にする必要があります。

これが「後工程」と呼ばれる領域で、具体的には以下の役割を担います。

- 物理的保護:衝撃や湿気、化学的腐食から守る

- 電気的接続:外部基板(PCB)との信号・電源接続

- 放熱:発熱を効率的に外へ逃がす

- 実装容易化:小さなチップを扱いやすくする

従来の後工程では、リードフレーム+樹脂封止やBGA(Ball Grid Array)などが主流でしたが、デバイスの小型化・高性能化に伴い、新たな手法が登場しています。

WLP/PLPの歴史

WLPの歴史

1990年代後半から研究・試作が始まり、2000年代前半には一部の製品で量産化されました。

特にFan-In WLP(チップサイズ内で配線を引き回すタイプ)は、スマートフォンやモバイル機器の小型チップで早くから採用されています。

例:2006〜2008年頃にはAppleのiPhoneやSamsungスマホのセンサー類に採用。

現状

今では成熟した量産技術で、スマホ向けアナログICやセンサーの多くがWLP化されています。

ただし、Fan-Out WLP(外側へ配線を広げるタイプ)は2010年代中頃から急速に普及(TSMCのInFOなど)。

PLPの歴史

PLPのコンセプト自体は2000年代に提案されましたが、実際の量産化は2015年以降の比較的新しい動きです。

主な理由は、パネルの反り(ワーページ)制御や装置標準化が難しかったため。

現状

まだ本格的量産は限られた企業のみ(Samsung、ASE、Nepesなど)で、技術開発段階にある部分も多いです。

特に大型AIチップやSiP向けのPLPは2020年代に入ってから本格化。

WLP → 10年以上前から量産化され、今では成熟技術。PLP → 実用量産はここ5〜10年以内に始まり、まだ発展途上だが次世代量産の本命候補。

WLP(Wafer Level Packaging)の特徴

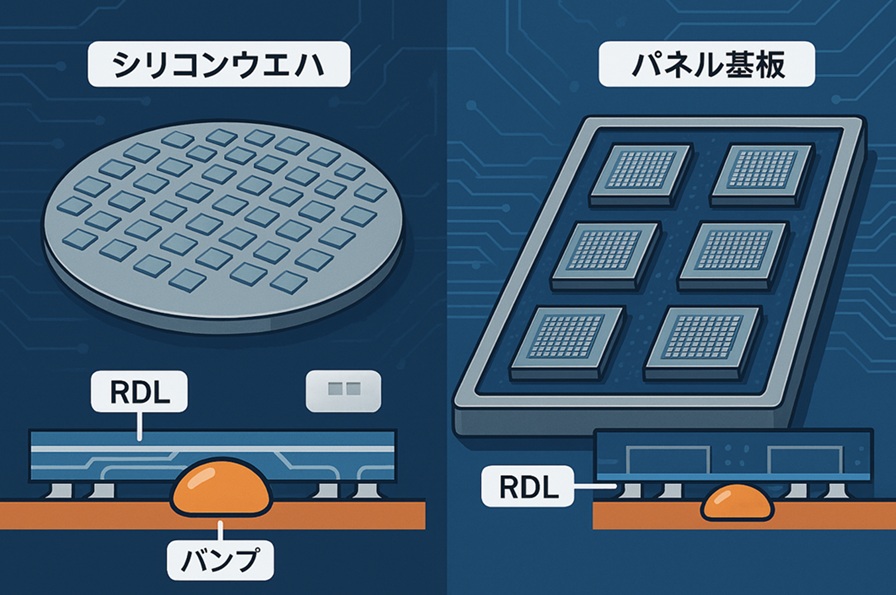

WLPは、ウエハの状態でパッケージングを行う手法です。

チップを個片化する前に、ウエハ全体に再配線(RDL)やバンプ形成を行い、その後にダイシングして完成品とします。

メリット

- 非常に薄型にできる(モバイル・ウェアラブル向け)

- 実装面積を最小化(CSPに近いサイズ)

- ウエハ単位で加工するため生産効率が高い

デメリット

- ウエハサイズの制約がある(通常12インチまで)

- 大型チップや異種チップ混載には不向き

主な用途:スマホ用RF部品、センサー、電源ICなど

PLP(Panel Level Packaging)の特徴

PLPは、円形のウエハではなく、矩形のパネル基板を使ってパッケージングする手法です。

チップをパネル上に並べ、その状態で再配線やバンプ形成を行います。

メリット

- パネルは矩形で面積利用効率が高い

- ウエハを超える大型基板で処理可能(スループット向上)

- 異種チップ混載や3D積層にも適応しやすい

デメリット

- パネルの反り(ワーページ)制御が難しい

- 装置・プロセスの標準化が進行中で成熟度は低め

主な用途:高性能パッケージ(AI・サーバー向け)、SiPなど

WLPとPLPの比較表

| 項目 | WLP | PLP |

| 加工単位 | 丸いウエハ | 矩形パネル |

| サイズ限界 | 12インチウエハ | 500×500mm級パネルも可能 |

| 対応範囲 | 小型チップ中心 | 大型・異種混載可能 |

| 生産性 | 高(成熟済) | 将来的により高い可能性 |

| 技術成熟度 | 高(量産多数) | 中(装置・規格整備中) |

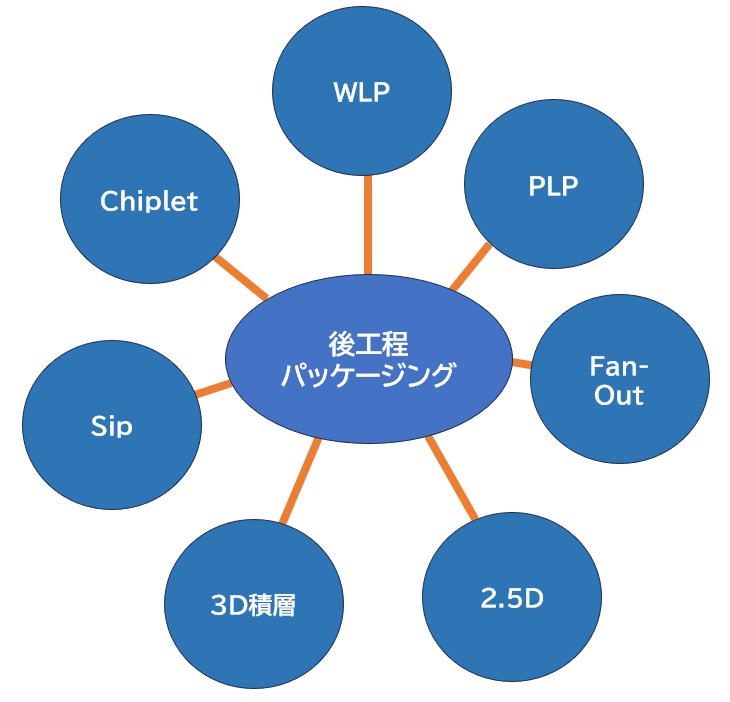

関連する次世代パッケージ技術

PLPやWLPは単独で使われるだけでなく、以下のような次世代技術と組み合わせることで性能向上が図られます。

- Fan-In / Fan-Out

Fan-In:チップサイズ内で配線を引き回し(コンパクト)

Fan-Out:チップ外側に配線を広げ、I/O数を増やす(PLPで多用)

- 2.5Dパッケージ(インターポーザ利用)

複数チップをシリコンや有機基板上で高速接続

- 3D積層パッケージ(TSV利用)

複数チップを上下に積み、シリコン貫通ビアで接続

- SiP(System in Package)

メモリ、ロジック、RFなど異種チップを1パッケージに統合

- Chipletアーキテクチャ

大型SoCを複数の小チップに分割し、パッケージ内で高速接続

まとめ ― 後工程の重要性はさらに高まる

半導体の性能向上は、微細化だけでは限界が見え始めています。そのため、後工程でのパッケージング技術が今後の差別化ポイントになります。

WLPはすでにスマホ・ウェアラブル分野で広く活用され、PLPは次世代の量産技術として開発が進んでいます。加えて、Fan-Outや3D積層などの技術が組み合わされることで、より高密度・高性能な製品が実現します。

これらの動向を押さえておくことは、半導体業界で働くエンジニアにとって必須の知識となるでしょう。