はじめに ― SoCとChipletの比較が重要な理由

半導体チップの性能向上は、長年にわたり「微細化」によって支えられてきました。

しかし、2nm世代を超えると、微細化だけでは性能とコストの両立が難しくなってきます。

製造プロセスはますます複雑になり、以下のような課題が顕在化しています。

- 歩留まりの低下(不良率の増加)

- マスク設計にかかるコストの増加

- 設計期間の長期化

従来のように、すべての機能を1枚のシリコン上に集約する「SoC(System on Chip)」の設計では、これらの課題に対応しきれなくなっています。

そこで注目は、「Chiplet(チップレット)」という設計アプローチです。

Chipletは、複数の小さなチップ(ダイ)を1つのパッケージ内で接続することで、柔軟性とスケーラビリティを確保しながら、性能・コスト・開発効率のバランスを取ることができます。

SoCとChipletは、設計思想、製造方法、コスト構造、そして適用される製品分野において大きく異なります。

本コラムでは、Rapidus、TSMC、Intel、AMD、NVIDIA、Samsungといった主要企業の取り組みを通じて、SoCとChipletの違いやそれぞれの役割について、実例を交えながらわかりやすく解説していきます。

SoCとChipletの違い

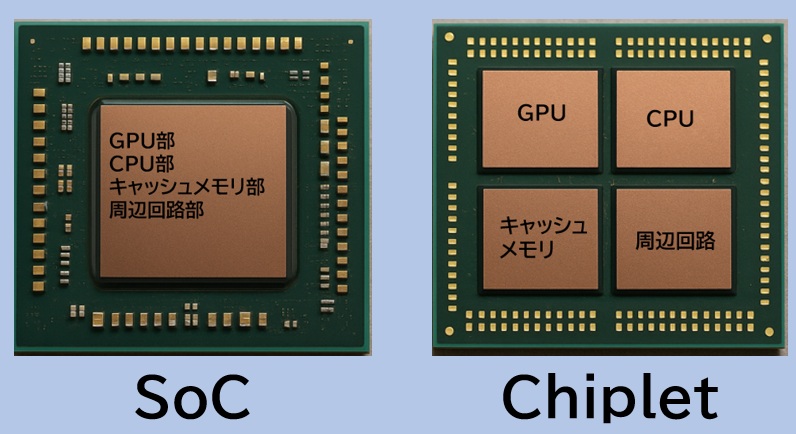

SoC(System on Chip)とは

SoCは、CPU・GPU・メモリコントローラ・I/O・AIアクセラレータなど、複数の機能ブロックを1枚のシリコンダイ上に集約した設計です。

スマートフォンなどのモバイル機器に広く使われており、高速な内部通信・省電力・小型化に優れています。

代表的な製品例:

- Apple「Aシリーズ」

- Qualcomm「Snapdragon」

SoCのメリット

SoCは、CPU・GPU・メモリ・I/Oなどの主要な機能が1枚のシリコン上に集約されているので、

- 各機能間の通信が短距離・高速・低消費電力で行えるため、全体としての効率が高くなる

- 性能・電力・コストのバランスを細かく調整しやすい

- 部品点数や基板面積を大幅に削減できるので小型・軽量なデバイスに最適

SoCのデメリット

- ダイが大きくなると歩留まりが低下しやすい

- 微細化が進むとマスク設計費が数百億円規模に膨らむ

- 一部の回路を変更するだけでも全体の再設計が必要

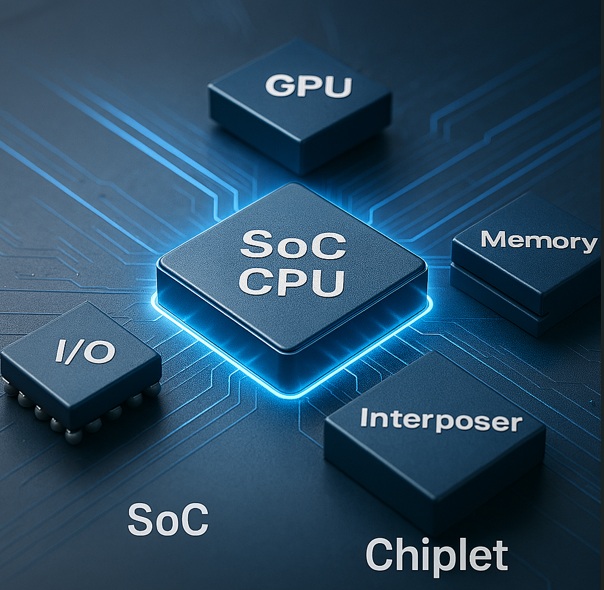

Chipletとは

Chipletは、CPU・GPU・I/Oなどの機能を複数の小さなダイに分割し、それらをパッケージ内で接続する設計手法です。

高速インターポーザや先端パッケージング技術を活用することで、SoCに近い性能を実現しつつ、柔軟性と製造効率を高めています。

代表的な製品例:

- AMD「Ryzen」「EPYC」

- Intel「Meteor Lake」

- NVIDIAの次世代GPU群

Chipletのメリット

- 小さなダイ単位で製造できるため歩留まりが向上

- IP(回路設計)の再利用がしやすく、開発効率が高い

- 異なるプロセスノードやベンダーの組み合わせが可能

Chipletのデメリット

- 高度なパッケージング技術が必要で実装コストが増加

- ダイ間通信により遅延や消費電力増のリスク

- SoCとは異なる設計思想のため新たな設計フローの習得が必要

SoCとChipletの用途

SoCとChipletは、それぞれの設計思想や構造の違いから、適する製品分野や市場が大きく異なります。

SoCが適している分野

SoCは、省電力・小型化・高集積が求められる製品に最適です。

具体的には以下のような分野で広く採用されています。

- スマートフォン

- タブレット

- IoT機器

- ウェアラブルデバイス

これらの製品は、筐体サイズやバッテリー持続時間に制約があるため、機能を1枚のダイに集約するSoCの特性が非常に有効です。

また、これらの市場は大量生産が前提となるため、初期投資(設計・マスク費用)を回収しやすく、SoCの経済性が活きてきます。

Chipletが適している分野

Chipletは、高性能・柔軟性・スケーラビリティが求められる分野に強みを発揮します。

主な用途は以下の通りです。

- データセンター向けCPU/GPU

- HPC(高性能計算)システム

- AIトレーニング用アクセラレータ

これらの分野では、大規模なダイ構成や多様な機能の組み合わせが必要となるため、Chipletのように機能ごとに分割して構成できる設計が有効です。

さらに、異なるプロセスノードやベンダーのIPを組み合わせることで、性能・コスト・開発効率の最適化が可能になります。

SoC→Chipletへ進む背景

近年、SoC(System on Chip)からChiplet(チップレット)への設計転換が加速しています。

その背景には、技術的・市場的な複数の要因が絡んでいます。

以下の4つのポイントは、特に重要な要素です。

微細化の限界

半導体の性能向上は長らく「微細化」によって支えられてきましたが、2nm世代以降では限界が顕在化しています。

EUV露光技術を用いても、歩留まりの低下や設計コストの高騰といった課題が避けられず、従来のSoC設計では経済性が成立しにくくなっています。

AI・HPCによる演算性能の急伸要求

ChatGPTのような大規模AIモデルや、スーパーコンピュータによる高性能計算(HPC)の需要が急増しています。

これらの用途では、膨大な演算能力とメモリ帯域が求められ、SoC単体では処理性能の伸びに限界があります。

Chipletは、複数の演算ダイを柔軟に組み合わせることで、スケーラブルな性能拡張が可能です。

コスト構造の変化

SoCでは、1枚の巨大なダイに全機能を集約するため、一部に不良があると全体が廃棄対象になります。

これに対し、Chipletは機能ごとに分割された小さなダイで構成されるため、不良部分のみの交換や再利用が可能となり、製造コストの最適化につながります。

設計スピードへの対応

市場では、製品の開発から投入までのスピードがますます重視されています。

Chipletは、既存のIP(回路設計資産)を再利用しやすく、設計のモジュール化によって開発期間を短縮できるため、迅速な製品展開に有利です。

主要企業/プロジェクトの動向(事例分析)

Rapidus(日本)

Rapidusは、2027年までに2nm世代の量産を目指す日本発の先端半導体企業です。

IBMとの技術提携を通じて最先端ロジック技術を導入し、国内外から優秀な人材を積極的に招聘しています。

日本の「半導体再興」を象徴する存在として、国家戦略の一環で事業が進められています。

戦略のポイント

- 初期フェーズでは、SoCの量産に注力し、国内製造基盤の確立を優先。

- 中長期的には、Chipletや3D積層技術に踏み込み、HPCやAI向け製品への展開を視野に。

- 経済産業省の支援を受け、段階的かつ戦略的に技術領域を拡張しています。

TSMC(台湾)

世界最大のファウンドリであるTSMCは、SoCとChipletの両方に対応できる製造体制を整えています。

Apple、NVIDIA、AMDなどの主要顧客を抱え、先端パッケージ技術「CoWoS」「InFO」「SoIC」で業界をリードしています。

戦略のポイント

- 2nm以降もSoC製造を継続しつつ、顧客ニーズに応じてChiplet統合を柔軟に提供。

- 「SoIC」技術により、TSV(シリコン貫通ビア)でダイ間を接続し、高速通信を実現。

- AI向け製品の需要増に対応し、パッケージング能力を強化中。

Intel(米国)

Intelは「IDM 2.0」戦略のもと、従来のCPU中心のSoC設計からChiplet構成への移行を加速しています。

競争力回復を目指す中で、Chipletは新たな技術的打開策として位置づけられています。

代表事例

- 「Meteor Lake」:CPU・GPU・I/Oをチップレット化し、柔軟な構成を実現。

- 「Foveros」:3D積層技術により、複数ダイを垂直方向に統合。

- 「Intel Foundry Services(IFS)」:外部顧客にもChipletベースの製造サービスを提供。

AMD(米国)

AMDは、Chiplet技術の先駆者的存在として知られています。

RyzenやEPYCシリーズでは、Chiplet構成を積極的に採用し、性能とコスト効率の両立を実現。結果として、サーバー市場でIntelに迫る競争力を獲得しました。

代表事例

- Ryzen CPU:8コアチップレットを複数組み合わせる構成で柔軟性を確保。

- EPYCサーバーCPU:多数のチップレットをインターポーザで統合し、高性能化。

- MI300シリーズ:CPUとGPUを統合したハイブリッド設計でAI/HPC向けに展開。

NVIDIA(米国)

GPU市場を牽引するNVIDIAも、Chiplet技術の導入を加速しています。

AI需要の急増に対応するため、GPU+Chiplet構成による拡張性と性能向上を追求しています。

戦略のポイント

- GPU本体はSoC的に設計されるが、HBM(高帯域メモリ)やI/OをChipletで構成する手法を拡大。

- AI向けGPU「H100」以降では、TSMCの「CoWoS」技術を活用し、大規模なChiplet統合を進展。

Samsung(韓国)

Samsungは、スマートフォン向けには従来通りSoC設計(Exynos)を維持しつつ、ファウンドリ事業ではChipletパッケージ技術の強化を進めています。

用途に応じた明確な住み分け戦略が特徴です。

戦略のポイント

- モバイル向けには、消費電力効率を重視したSoC設計を継続。

- サーバーやHPC分野では、「X-Cube」技術を活用し、3D Chiplet統合を推進。

国家プロジェクトとの連動 ― 技術戦略と政策支援の融合

SoCからChipletへの技術転換は、企業単独の取り組みにとどまらず、各国の国家プロジェクトと密接に連動しています。

- 日本:Rapidusを軸にした再興戦略

日本では、Rapidusを中心に2nm世代のSoC量産と将来的なChiplet基盤の整備が進められています。

経済産業省の支援のもと、製造・設計・人材の三位一体で国家戦略として推進されており、国内半導体産業の再興を目指す象徴的なプロジェクトです。

- 米国:CHIPS Actによる産業支援と規格整備

米国は「CHIPS Act」により、IntelやTSMCなどの国内製造拠点の整備を支援するとともに、Chipletの規格標準化にも注力しています。

これにより、異なる企業・プロセス間での互換性と再利用性を高め、エコシステム全体の効率化を図っています。

- 欧州:EU Chips Actで設計・製造の両面強化

EUは「EU Chips Act」を通じて、設計力の強化と製造基盤の拡充を同時に進めています。

SoCとChipletの両方に対応できる体制を目指し、研究開発・人材育成・インフラ整備を包括的に支援しています。

- 中国:独自開発と技術探索の並行推進

中国は、独自のSoC設計・製造技術の確立を進める一方で、Chiplet技術の導入と応用可能性も模索しています。

国家主導の半導体強化政策の中で、自給率向上と技術多様化の両立を図る動きが見られます。

今後の方向性

半導体設計は、SoCとChipletという異なるアプローチがそれぞれの強みを活かしながら進化しており、今後は両者の融合によるハイブリッド設計が主流になると見込まれています。

- SoCの今後:省電力・小型化が求められる分野で不可欠

SoCは、スマートフォン・IoT機器・車載エレクトロニクスなど、消費電力とサイズ制約が厳しい分野で今後も中心的な役割を担います。

これらの製品では、機能を1枚のダイに集約することで、高集積・低消費電力・高速通信を実現できるため、SoCの利点が最大限に活かされます。

- Chipletの今後:高性能・柔軟性が求められる分野で急成長

Chipletは、AIサーバー・HPC(高性能計算)・クラウドインフラ・スーパーコンピュータなど、演算性能とスケーラビリティが重視される分野で急速に拡大しています。

複数のダイを組み合わせることで、性能・開発効率・製造歩留まりのバランスを取りながら、柔軟なシステム構成が可能になります。

- 融合モデルの台頭:SoC+Chipletによるハイブリッド設計

今後は、SoCとChipletの長所を組み合わせたハイブリッド設計が主流になると予想されます。

たとえば、CPU部分はSoC的に統合して高効率を確保しつつ、GPU・I/O・メモリなどの周辺機能はChiplet化することで、柔軟性と拡張性を両立する構成が増えています。

まとめ

SoCとChipletは「対立する技術」ではなく「相補関係」にあります。

- SoCは依然としてスマホやIoTで重要。

- ChipletはAIやHPC分野で必要不可欠。

- 主要企業は両者を組み合わせる戦略を採用しており、Rapidusもその流れに沿った道を歩み始めています。

次世代半導体の競争は、単なる微細化競争ではなく、設計アーキテクチャとパッケージ技術の総合力に移行しています。SoCとChipletの双方を理解することが、今後の半導体を語るうえで欠かせない視点となるでしょう。