はじめに:今、なぜ光チップレットが注目されているか

半導体は長年、性能向上を支えてきた微細化は先端ノードで限界が見え始め、従来の延長線だけでは十分な進化を維持できなくなってきました。

こうした状況の中で、新たな成長軸として存在感を急速に高めているのが「チップレット化」と「光技術の導入」です。

関連記事:光電融合技術の基礎知識・ロードマップと主要プレイヤー:2035年の展望

チップレットは、機能ごとに分割された半導体ダイを高密度に接続することで、性能・コスト・歩留まりのバランスを最適化するアーキテクチャとして、すでにCPUやAIチップの分野で広く採用が進んでいます。

しかし、その一方で、チップ間通信の電力消費や帯域の限界が顕在化し、特にAIやデータセンター用途においては「電力あたりの通信効率」が重大なボトルネックとなっています。

この課題を根本から解決する技術として期待されているのが「光チップレット」です。

電気信号ではなく光信号を用いたデータ伝送により、従来比で桁違いの帯域密度と低消費電力を実現でき、AIインフラやクラウド基盤の設計思想そのものを変える可能性を持っています。

近年は、シリコンフォトニクスの成熟や2.5D/3D実装など先進パッケージ技術の進化に加え、大手半導体企業やクラウド事業者の積極投資が重なり、光チップレットは研究段階から実用化フェーズへと移行しつつあります。

2026年以降の試験導入、2028年以降の量産立ち上げ、そして2030年前後の本格普及というシナリオが現実味を帯びてきました。

本コラムでは、光チップレットの技術構造、製造プロセス、主要プレイヤー、そして市場動向までを体系的に整理します。

「チップレット」と「光チップレット」の違い

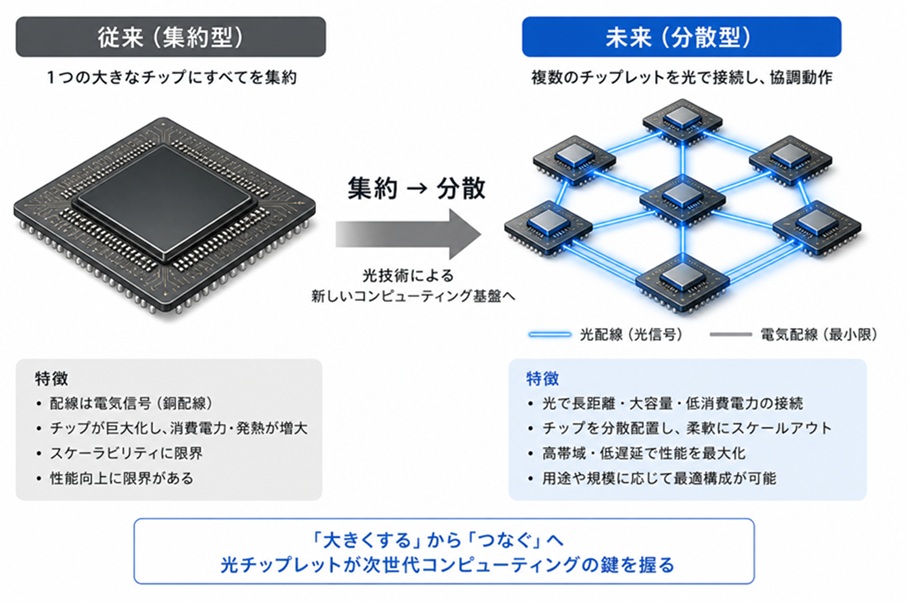

半導体の進化が「微細化中心」から「接続技術中心」へと移りつつある中で、チップレットはその変化を象徴するアーキテクチャとして広く注目されています。

そして現在、そのチップレット自体が次の段階へ進み、電気配線を前提とした従来型から、光技術を取り込んだ新しい形態へと拡張され始めています。

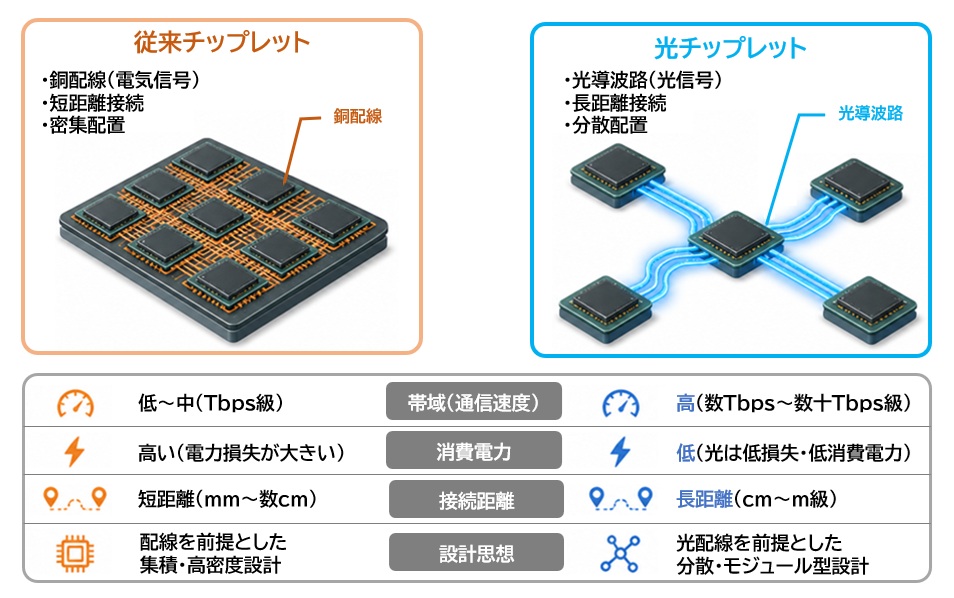

通常のチップレットと光チップレットの違いを、構造面と本質面の両方から整理します。

通常のチップレット

通常のチップレットとは、CPUコア、GPUコア、I/O、メモリコントローラなどの機能を個別の小さなダイ(チップレット)として設計し、それらを1つのパッケージ内で高密度に接続する技術です。

通常のチップレットは、CPUコア、GPUコア、I/O、メモリコントローラなどの機能を小さなダイとして分割し、それらを1つのパッケージ内で高密度に接続する技術です。

モノリシックSoCと比べると、以下のような利点があります。

- 歩留まりの向上

大型ダイを避け、小型ダイの組み合わせとすることで製造効率が向上します。 - コスト最適化

先端ノードと成熟ノードを組み合わせる「ヘテロジニアス統合」が可能です。 - 設計の柔軟性

IP単位で再利用でき、開発期間の短縮にもつながります。

一方で、チップレット間の接続は電気信号(銅配線)に依存しているため、次のような課題が顕在化しています。

- 帯域幅の制約(配線密度・信号干渉)

- 消費電力の増大(高速I/Oほど電力が増える)

- 伝送距離の限界(パッケージ外では急激に劣化)

特にAIやHPCでは通信量が急増しており、「電気I/Oの限界」がシステム全体の性能を左右する状況になっています。

光チップレット

光チップレットは、チップレット間通信を電気ではなく光で行うことを前提とした次世代アーキテクチャです。

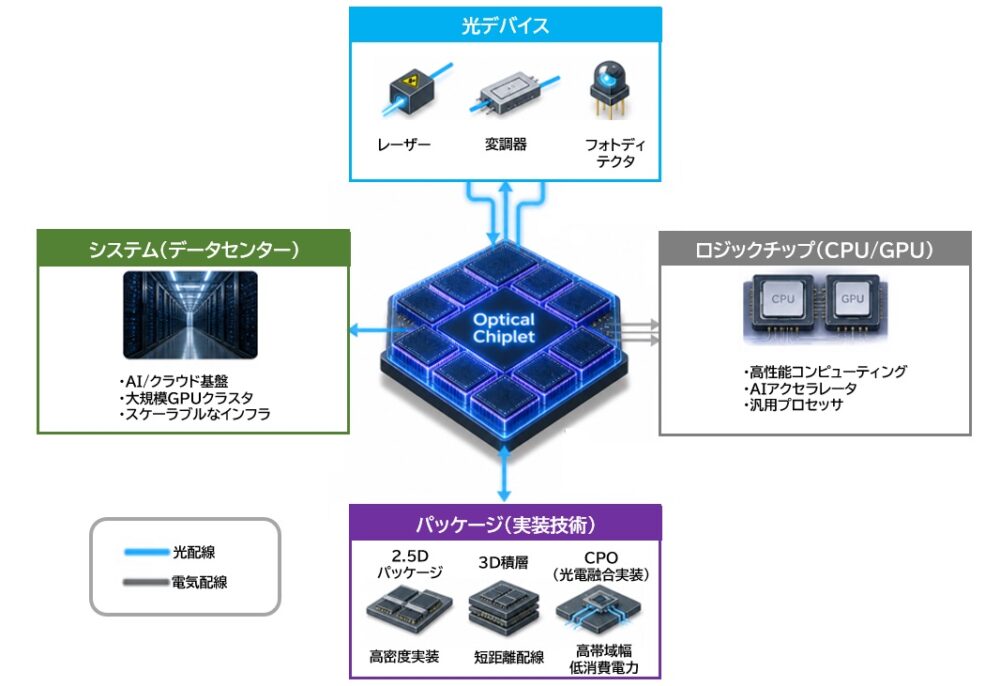

シリコンフォトニクスを基盤に、レーザー、変調器、フォトディテクタ、光導波路などの光デバイスをチップレットとして統合します。

主な特徴は以下の通りです。

- 超高帯域:波長多重(WDM)により、1本の光配線で複数データを同時伝送できます。

- 低消費電力:長距離・大容量通信で電気配線より高効率です。

- 長距離伝送:パッケージ内に限らず、ボード間・ラック間へ容易に拡張できます。

光チップレットは単なる高速I/Oの置き換えではなく、パッケージ設計そのものを変える可能性を持っています。

従来の「近接配置が前提」から、「分散配置+光接続」へと設計の自由度が大きく広がります。

決定的な違い

通常のチップレットと光チップレットの違いは、通信方式の違いにとどまりません。

本質的には システム設計の前提が変わる 点にあります。

●比較表(通常のチップレット vs 光チップレット)

| 項目 | 通常のチップレット | 光チップレット |

| 接続方式 | 電気配線 | 光配線 |

| 帯域密度 | 制約あり | 非常に高い |

| 消費電力 | 高い(特に長距離) | 低い(距離に強い) |

| 伝送距離 | パッケージ内中心 | パッケージ外へ拡張可能 |

| 設計思想 | 集約型(近接配置) | 分散型(リソース分離) |

特に大きな違いは 「距離に対する制約」 が劇的に変わることです。

電気配線は距離が伸びるほど信号品質が悪化し、電力効率も低下します。 一方、光は距離による劣化が小さいため、チップを物理的に離して配置できます。

これにより、次のような新しい設計が可能になります。

- コンピュートとメモリの分離(Disaggregated Architecture)

- ラック全体を1つの巨大チップのように扱う構造

- AIクラスタのスケーラビリティ向上

つまり光チップレットは、単なる技術進化ではなく、 半導体からシステム全体へと広がるパラダイムシフト を引き起こす存在です。

光チップレットの製造方法

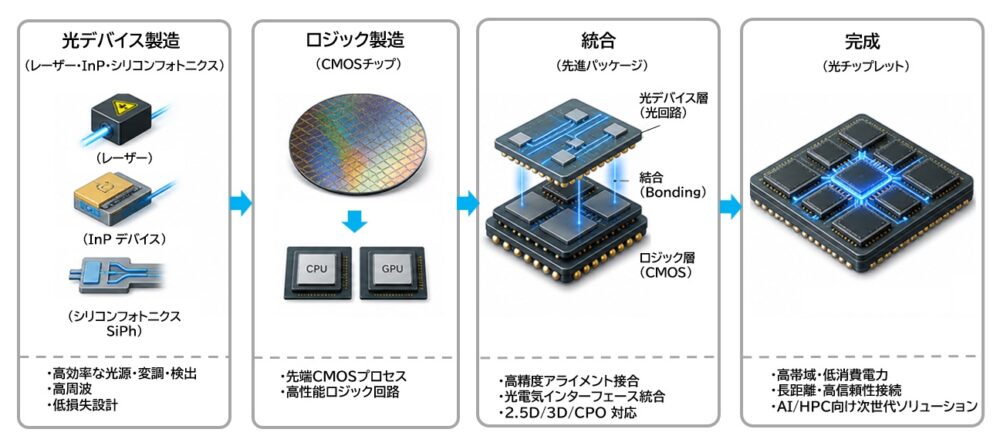

光チップレットは、従来の半導体のように単一プロセスで完結するものではありません。

「異種材料」「異なる製造ライン」「高度な統合技術」が組み合わさって初めて成立するため、製造の本質は個々の技術の高度化だけでなく、それらをいかに高精度に統合するかにあります。

基本的な製造フロー

光チップレットの製造は、大きく次の3段階で構成されます。

- 光デバイスの製造(フォトニクス領域)

- ロジックチップの製造(CMOS領域)

- 両者の統合(パッケージング領域)

光デバイスとロジックは最適プロセスがまったく異なるため、単一ファウンドリで完結するケースは限定的です。

その結果、サプライチェーンは自然と「前工程+後工程+光デバイス」という三層構造へと分業化が進みます。

光デバイス(異種材料)

光チップレットの中核となるのが光デバイスです。

ここでは、光を生成・制御・検出するための機能が実装されます。

主な構成要素は以下の通りです。

- レーザー(光源)

- 変調器(電気→光変換)

- フォトディテクタ(光→電気変換)

- 光導波路(光の伝送路)

特に重要なのは、材料がロジック半導体とは大きく異なる点です。

- インジウムリン(InP):高効率レーザー

- ガリウム砒素(GaAs):高速光デバイス

- シリコンフォトニクス:CMOSとの親和性が高い

これらを単一基板にまとめて形成することは難しく、現実的には 異種材料の接合(ヘテロジニアス統合) が前提となります。

ここが光チップレット特有の難しさであり、同時に競争力の源泉でもあります。

ロジック(通常半導体)

演算や制御を担うロジックチップは、従来通り最先端のCMOSプロセスで製造されます。

- 3nm / 2nmなどの先端ノードによる高性能化

- 高速SerDesやPHYとの連携

- HBMなどメモリとの統合

光デバイスとロジックは、無理に一体化するのではなく、それぞれを最適条件で製造し、後工程で接続する という思想が基本になります。

統合

光チップレットの価値の中心であり、同時に最大の難関がこの「統合」です。

電気的な接続だけでなく、光信号として正確に結合させる必要があるため、要求される精度は桁違いに高くなります。 この工程の成否が、光チップレットの量産可否を左右します。

実装技術

統合には、以下のような先進パッケージング技術が用いられます。

- 2.5D実装(インターポーザ)

シリコンインターポーザ上で電気配線と光導波路を共存させる構造です。 - 3D積層(Hybrid Bonding)

ダイ同士を直接接合し、極めて短距離で高密度接続を実現します。 - CPO(Co-Packaged Optics)

光エンジンとASICを同一パッケージに統合する方式です。 - 光ファイバー直接結合

パッケージ外との光接続を担う重要な技術です。

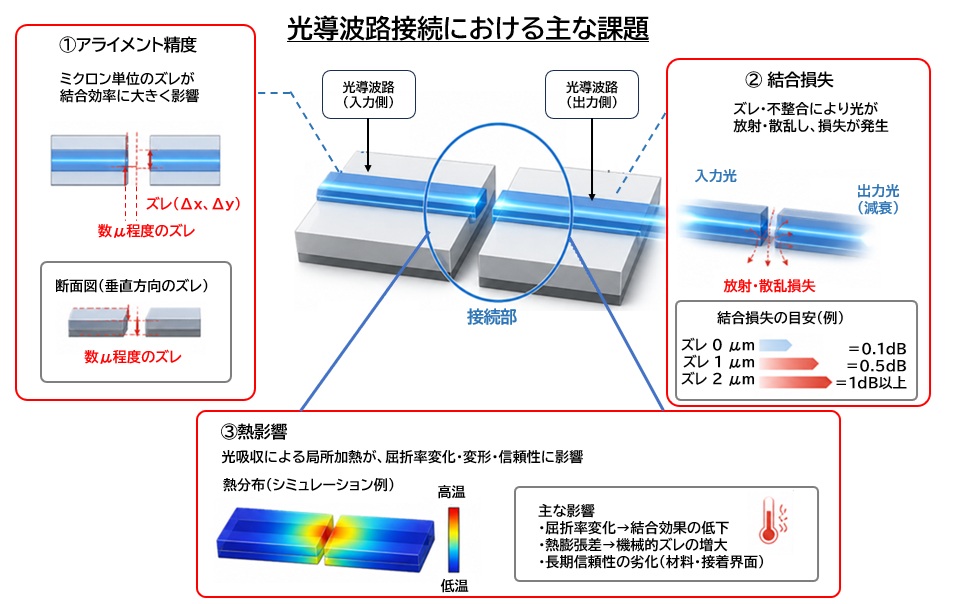

最大の難関

光チップレットの量産化における最大の課題は、光結合精度 と 熱管理 にあります。

- アライメント精度

光導波路同士の位置ズレは数ミクロン以下で制御する必要があります。 - 結合損失(Insertion Loss)

光接続部での損失をいかに抑えるかが重要です。 - 熱影響

レーザーやロジックの発熱により光特性が変動するため、熱設計が不可欠です。 - 量産性

高精度アライメントを低コストで量産することが最大のボトルネックです。

この「位置合わせ」と「熱安定性」を克服できなければ、どれほど優れたデバイスでも実用化は困難です。

技術トレンド

現在の技術開発は、上記の課題を解決する方向に集中しています。

- モノリシック化への挑戦

シリコンフォトニクス上にレーザーを直接形成する試みが進んでいます。

関連記事:モノリシック3D DRAMは本当に来るのか:2026年時点の技術・市場・勝者予測 - パッシブアライメント技術

自然に位置が合う構造設計により、量産性を高めるアプローチです。 - 光I/Oの標準化

電気I/Oのように扱えるインターフェースを確立する動きが加速しています。 - 低消費電力レーザー

データセンター用途に最適化した光源の開発が進んでいます。 - 光電融合設計(Co-Design)

チップ設計とパッケージ設計を一体で最適化する手法が重要性を増しています。

これらの進展により、光チップレットは研究テーマから、量産を前提とした実装技術競争へと移行しつつあります。

実用化企業とサプライヤー

光チップレットは、単一企業だけで完結する技術ではありません。

「光デバイス」「ロジック半導体」「パッケージング」「設計ツール」など、多層的なプレイヤーが連携することで初めて成立します。

そのため競争の本質は、個社の技術力だけでなく、どのようなエコシステムを構築できるか にあります。

コアプレイヤー(最重要)

光チップレット領域は、大きく4つのプレイヤー群に分類できます。

それぞれが異なる役割を担いながら、全体として1つのシステムを形成しています。

光チップレット開発

光チップレットの中核技術であるシリコンフォトニクスや光I/Oを開発する企業群です。

- Intel

シリコンフォトニクスの先行企業で、CPO(Co-Packaged Optics)の実装を積極的に推進しています。

自社CPUとの統合を前提とした垂直統合型戦略が特徴です。 - Cisco Systems

通信機器大手として、データセンター向け光I/Oの実用化をリードしています。

Acacia買収により光技術を内製化しました。 - Ayar Labs

光I/Oチップレットの代表的スタートアップで、電気配線を置き換える光インターコネクト技術を提供しています。 - Lightmatter

光ベースのAIアクセラレータを開発し、光チップレットの新たな応用領域を切り開いています

半導体・パッケージ

ロジック製造や先進パッケージングを担う企業群で、光チップレットの量産可否を左右する重要なポジションです。

- TSMC

CoWoSやSoICなどの先進パッケージ技術を提供し、光統合への拡張を進めています。

幅広い顧客エコシステムが強みです。 - Samsung Electronics

HBMと先進パッケージを組み合わせた統合戦略を展開し、光技術との融合も視野に入れています。 - ASE Group

OSAT最大手として、異種チップ統合の量産基盤を担います。光実装の量産化において重要な役割を果たします。 - Amkor Technology

グローバルな後工程プレイヤーであり、光チップレットの実装を支える存在です。

ネットワーク / ASIC

実際に光チップレットを採用し、データセンターやAI用途で活用する企業群です。

需要側として市場拡大の主導役となります。

- NVIDIA

AI GPUのリーダーとして、チップ間通信のボトルネック解消に強いニーズを持ち、光I/Oの導入が期待されています。 - Broadcom

スイッチASICと光モジュールの両方を手掛け、CPOの商用化を推進しています。 - Marvell Technology

データセンター向けインターコネクトに強みを持ち、光接続技術の統合を進めています。 - Google / Amazon / Microsoft

ハイパースケーラーとして、自社データセンターの電力効率改善を目的に光技術への投資を加速しています。

EDA / IP

光チップレットの設計には、電子回路に加えて光設計が必要となるため、EDA/IP企業の役割が一段と重要になります。

- Synopsys

フォトニクス対応の設計ツールを提供し、光電融合設計を支援しています。 - Cadence Design Systems

パッケージとチップの統合設計(Co-Design)を可能にするプラットフォームを展開しています。 - Ansys

光・熱・電気のマルチフィジックス解析を提供し、設計精度向上に貢献しています。

サプライチェーン構造

光チップレットのサプライチェーンは、従来の半導体よりも複雑で、光デバイス・ロジック・パッケージ・システム の4層が密接に連携することで成立します。

それぞれの層が異なる技術要件を持つため、どの企業がどのレイヤーを押さえるかが競争力に直結します。

光デバイス層

光チップレットの“光”そのものを作る層であり、最も専門性が高い領域です。

レーザー、変調器、フォトディテクタ、光導波路など、光信号を生成・制御・検出するデバイスを製造します。

● この層が担う役割

- 光源(レーザー)の製造

- 光変調器・受光器の形成

- シリコンフォトニクス基板の製造

- InP / GaAs など異種材料の加工

- 光導波路の形成と低損失化

光チップレットの性能は、この層の技術力に大きく依存します。

特にレーザーの効率、変調器の速度、光導波路の損失は、システム全体の帯域・電力効率を左右します。

● 主な企業

- Intel(シリコンフォトニクス)

- Ayar Labs(光I/Oチップレット)

- Lumentum / Coherent(レーザー)

- Infinera(InPベース光デバイス)

- GlobalFoundries(シリコンフォトニクス製造)

- Tower Semiconductor(フォトニクス対応プロセス)

ロジック層

AI演算や制御を担うロジックチップを製造する層です。

光デバイスとは異なり、最先端CMOSプロセスで製造されます。

● この層が担う役割

- GPU/ASIC/AIチップの製造

- 高速SerDesやPHYの実装

- HBMなどメモリとの統合

- 光I/Oと連携するロジック設計

光チップレットは光デバイスとロジックを後工程で統合するため、ロジック側は「光接続を前提とした設計」が求められます。

● 主な企業

- TSMC(3nm/2nmロジック製造)

- Samsung Electronics(ロジック+HBM)

- Intel Foundry Services(先端ロジック+光技術)

- NVIDIA / AMD / Broadcom(ASIC・GPU)

- Micron / SK hynix(HBM)

パッケージ層

光デバイスとロジックを“つなぎ合わせる”層であり、光チップレットの量産可否を決める最重要領域です。

● この層が担う役割

- 2.5D/3D実装(CoWoS、SoICなど)

- 光デバイスとロジックの高精度アライメント

- 光導波路と電気配線の共存設計

- CPO(Co-Packaged Optics)の統合

- 光ファイバーとの結合構造の形成

光結合は数ミクロン以下の精度が必要で、熱変動にも強い構造が求められます。

この層の技術力が、光チップレットの歩留まりとコストを大きく左右します。

● 主な企業

- TSMC(CoWoS / SoIC)

- ASE Group(OSAT最大手)

- Amkor Technology(先進パッケージ)

- Intel(EMIB / Foveros)

- SPIL(光対応パッケージ)

システム層

光チップレットを実際の製品として組み込み、データセンターやAIクラスタで運用する層です。

ここが“需要側”であり、市場成長の主導役となります。

● この層が担う役割

- AI/HPCシステムへの光I/O統合

- データセンターの電力効率改善

- ラック内・ラック間の光接続設計

- ネットワーク機器へのCPO搭載

- 大規模クラスタのアーキテクチャ設計

光チップレットの普及は、この層の意思決定によって一気に加速します。

特にハイパースケーラーは電力コスト削減のインセンティブが大きく、採用が進むと市場が一気に立ち上がります。

● 主な企業

- NVIDIA(AI GPU+光I/O統合)

- Broadcom(スイッチASIC+CPO)

- Marvell(データセンター向けASIC)

- Google / Amazon / Microsoft(ハイパースケーラー)

- Cisco / Arista(ネットワーク機器)

サプライチェーンの本質

光チップレットのサプライチェーンは、光デバイス → ロジック → パッケージ → システム という4層が密接に連携することで成立します。

そして現在の潮流は、

- 光技術の内製化

- パッケージングの囲い込み

- 設計〜実装の一体化(Co-Design)

といった 準垂直統合 へ向かっています。

つまり、光チップレット市場ではどのレイヤーまで支配できるかが競争力を決める という構造が明確になりつつあります。

実用化ロードマップと市場

光チップレットは、すでに研究段階を超え、「いつ・どの領域から本格普及するか」というフェーズに入っています。

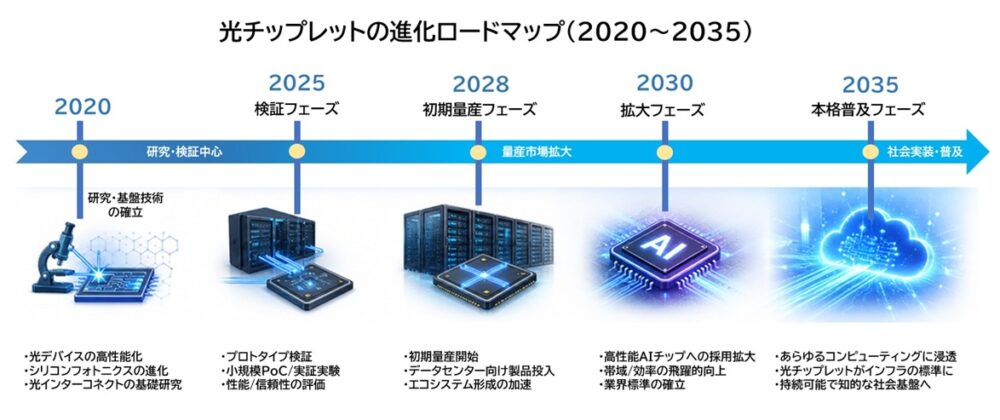

技術ロードマップ

~2025(検証・限定導入フェーズ)

この段階では、光チップレットは主に実証実験および限定的な商用導入にとどまります。

- CPO(Co-Packaged Optics)の試験導入開始

- データセンター向けスイッチASICへの限定採用

- 光I/Oチップレットの評価ボードレベルでの検証

- パッケージング技術(2.5D/3D)の高度化

量産性とコストがまだ成熟していないため、導入は電力効率改善の効果が大きい一部用途に限定されます。

2026〜2028(初期量産フェーズ)

光チップレットが実用化へ踏み出す最初の転換点です。

- CPOの本格採用(スイッチ、AIアクセラレータ)

- 光I/Oが電気I/Oの一部を代替

- ハイパースケーラーによる採用拡大

- OSAT・ファウンドリによる量産ライン整備

このフェーズでは、以下が大きく進展します。

- パッシブアライメント技術の確立

- 結合損失の低減

- 設計ツール(EDA)の成熟

結果として、「特定用途では電気配線より明確に優位」という状態に到達します。

2028〜2030(拡大フェーズ)

この時期に、光チップレットは市場の主流技術の一つへと成長します。

- AI/HPCチップでの標準採用

- メモリ(HBM)との光接続の検討・一部実装

- ラック内・ラック間の光接続統合

- 光I/Oのインターフェース標準化

チップ内の一部機能ではなく、システム全体設計に組み込まれる段階 に入ります。 データセンターのアーキテクチャが変わり始める重要な時期です。

2030以降(本格普及・構造転換フェーズ)

2030年以降は、光チップレットがインフラの前提技術へと移行します。

- コンピュートとメモリの完全分離(Disaggregation)

- ラックスケールコンピューティングの一般化

- 光ベースのデータセンターアーキテクチャ

- 一部でモノリシック光統合の実用化

この段階では、もはや「光を使うかどうか」ではなく、光を前提にシステムを設計する世界へと移行します。

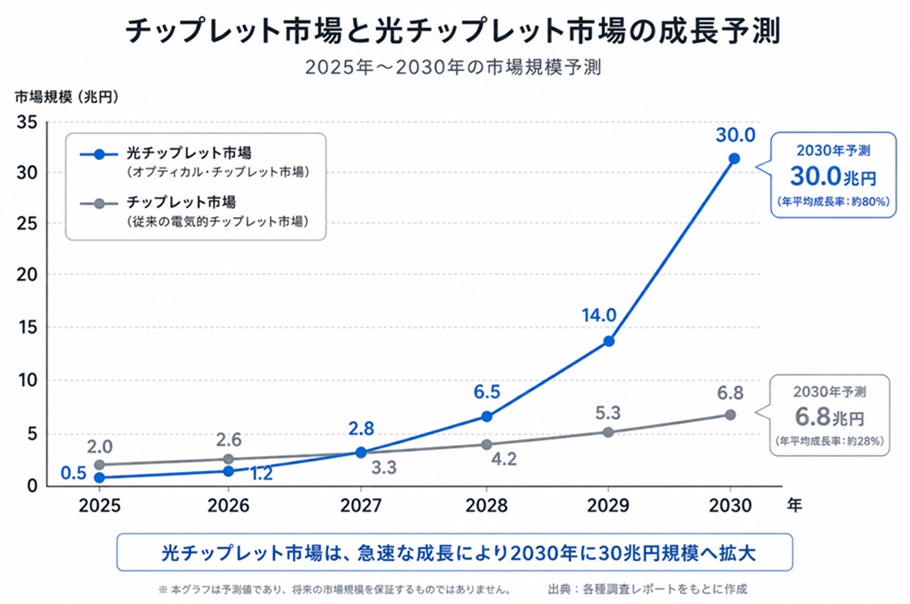

市場規模

チップレット市場

チップレット全体の市場は、すでに急成長フェーズにあります。

- 2025年:約5兆円規模

- 2030年:約10〜15兆円規模

成長の主因は、

- AI半導体需要の爆発的拡大

- 先端ノードコストの高騰

- ヘテロジニアス統合の普及

光チップレットは、この巨大市場の中で 最も高付加価値の領域 を形成します。

光チップレット関連

光チップレット単体、光I/O、CPO、光デバイスなどを含む市場は、より急峻な成長を見せます。

- 2025年:数千億円規模(立ち上がり)

- 2028年:1〜2兆円規模

- 2030年:3〜5兆円規模

特に成長を牽引するのは、

- データセンター向け光インターコネクト

- AIクラスタ内通信

- 高速ネットワーク機器

用途別

用途別に見ると、導入の優先順位は明確です。

① データセンター(最優先)

- 最大の電力消費領域

- 投資回収が早い

- ハイパースケーラー主導

② AI / HPC

- 帯域要求が極めて高い

- GPU間通信のボトルネック解消

③ 通信インフラ

- 5G/6Gバックボーン

- 高速スイッチ・ルーター

④ エッジ / 車載(後発)

- コスト制約が大きい

- 小型化・低消費電力が課題

本章のポイント

光チップレット市場の本質は、「徐々に広がる」のではなく、特定領域から一気に拡大する“非連続成長”にあります。

- 初期はデータセンターに集中

- 量産化でコスト低下

- その後、他用途へ波及

この構造を理解することが、重要となります。

まとめ

本コラムでは、光チップレットの構造・製造・プレイヤー・市場までを一貫して整理してきました。

それらを踏まえ、技術の本質とビジネス上の意味を端的にまとめます。

技術の本質

光チップレットの本質は、「電気配線の限界を光で置き換える」という単純な話ではありません。

より本質的には、“距離の制約からの解放”にあります。

従来の半導体設計では、以下が前提でした。

- チップは近くに配置しなければならない

- 距離が伸びるほど性能と効率が悪化する

- そのため機能を1つのパッケージ内に集約する

しかし光チップレットでは、この前提が大きく変わります。

- 距離が伸びても帯域と効率を維持できる

- チップや機能を分散配置できる

- システム全体を柔軟に再構成できる

つまり、光チップレットは「集約から分散へ」という設計思想の転換をもたらします。

これは単なる性能改善ではなく、コンピューティングアーキテクチャそのものの変革です。

なぜ重要か

この技術が注目される最大の理由は、AI時代のボトルネックを直接的に解決する唯一の有力手段だからです。

現在のAIインフラでは、以下の問題が顕在化しています。

- GPU性能の向上に対して通信が追いつかない

- データ移動の電力が計算電力を上回り始めている

- データセンター全体の消費電力が急増している

これらはすべて「電気配線」に起因する問題です。したがって、どれだけ演算性能を高めても、通信がボトルネックである限りスケールは頭打ちになります。

光チップレットはこの問題に対し、

- 帯域を桁違いに引き上げ

- 電力効率を改善し

- スケーラビリティを確保する

という形で、根本的な解決策を提供します。

言い換えれば、光チップレットはAI・クラウド時代を成立させるためのインフラ技術です。これが重要視される理由です。

本コラムを通じて、光チップレットを単なる新技術として捉えるのではなく、次世代インフラの基盤となる構造変化として理解することです。

これを起点に、半導体・データセンター・ネットワークの各産業は、今後大きく再編されていくことになります。